- 快召唤伙伴们来围观吧

- 微博 QQ QQ空间 贴吧

- 文档嵌入链接

- 复制

- 微信扫一扫分享

- 已成功复制到剪贴板

低功耗超大规模集成电路设计介绍

展开查看详情

1 .Introduction

2 .Why Worry about Power? Total Energy of Milky Way Galaxy: 10 59 J Minimum switching energy for digital gate (1 electron@100 mV): 1.6 10 -20 J (limited by thermal noise) Upper bound on number of digital operations: 6 10 78 Operations/year performed by 1 billion 100 MOPS computers: 3 10 24 Energy consumed in 180 years , assuming a doubling of computational requirements every year (Moore’s Law). The Tongue-in-Cheek Answer

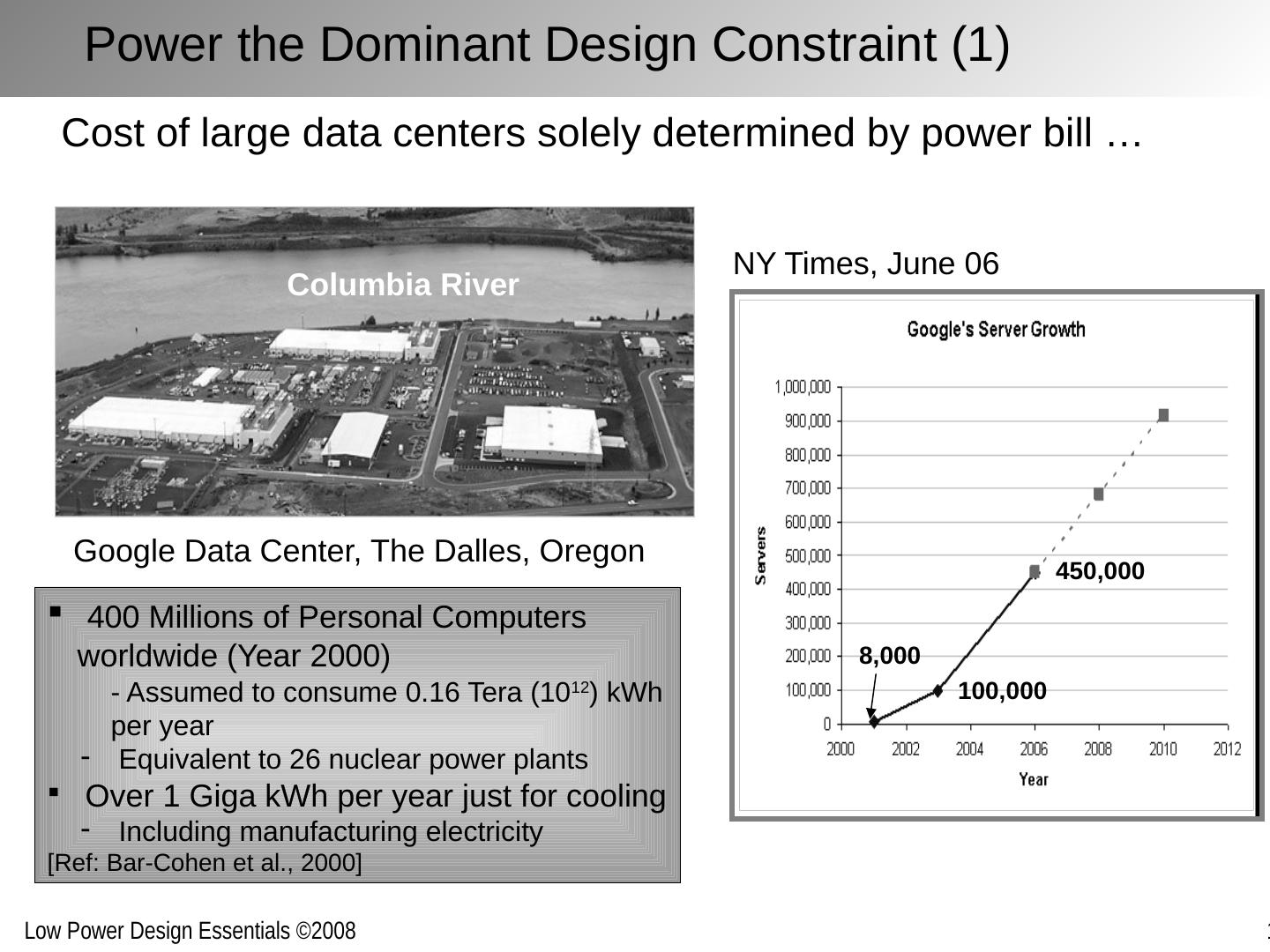

3 .Power the Dominant Design Constraint (1) Cost of large data centers solely determined by power bill … Google Data Center, The Dalles, Oregon Columbia River 8,000 100,000 450,000 NY Times, June 06 400 Millions of Personal Computers worldwide (Year 2000) - Assumed to consume 0.16 Tera (10 12 ) kWh per year Equivalent to 26 nuclear power plants Over 1 Giga kWh per year just for cooling Including manufacturing electricity [Ref: Bar -Cohen et al., 2000]

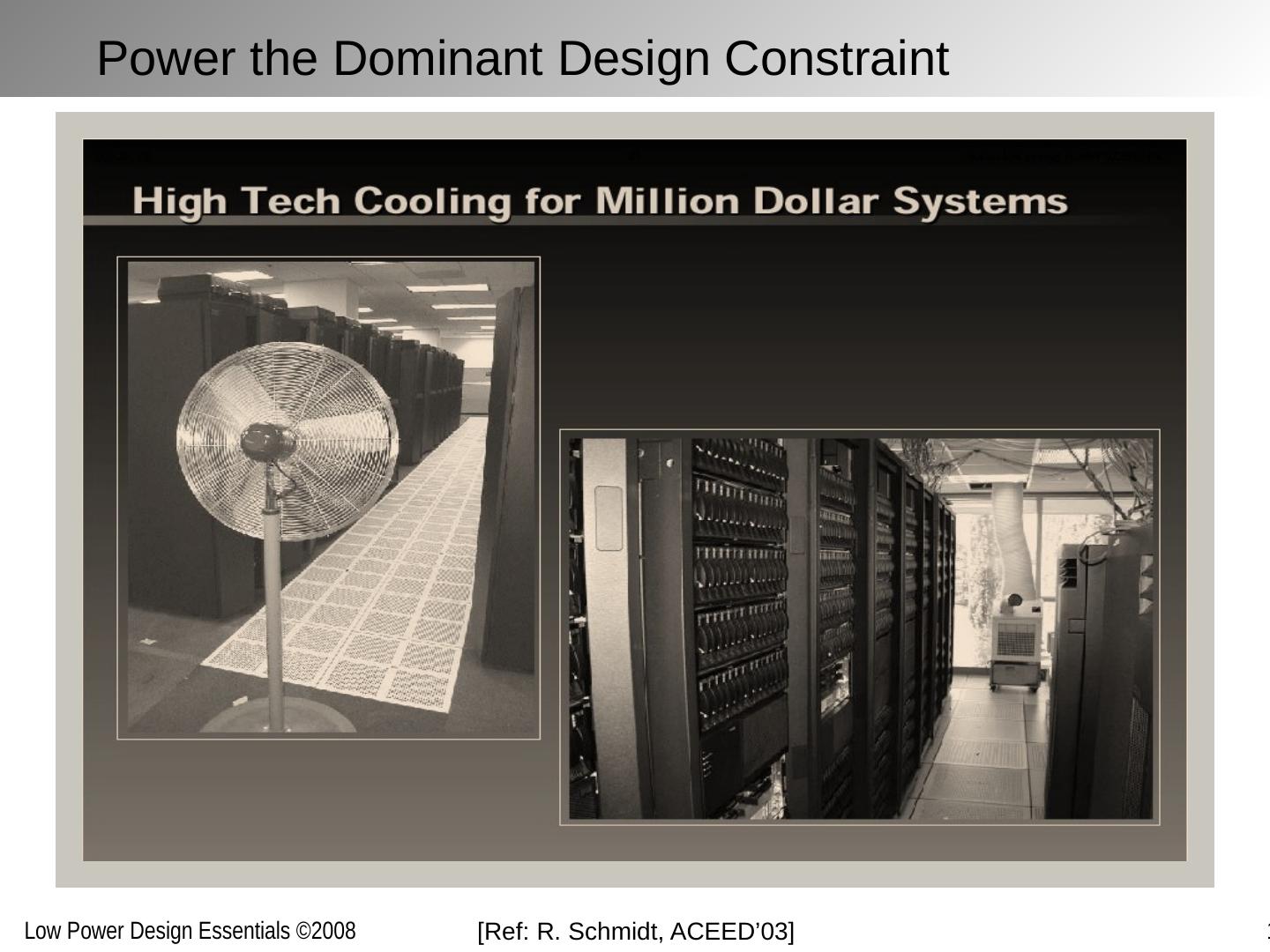

4 .Power the Dominant Design Constraint [Ref: R. Schmidt, ACEED’03]

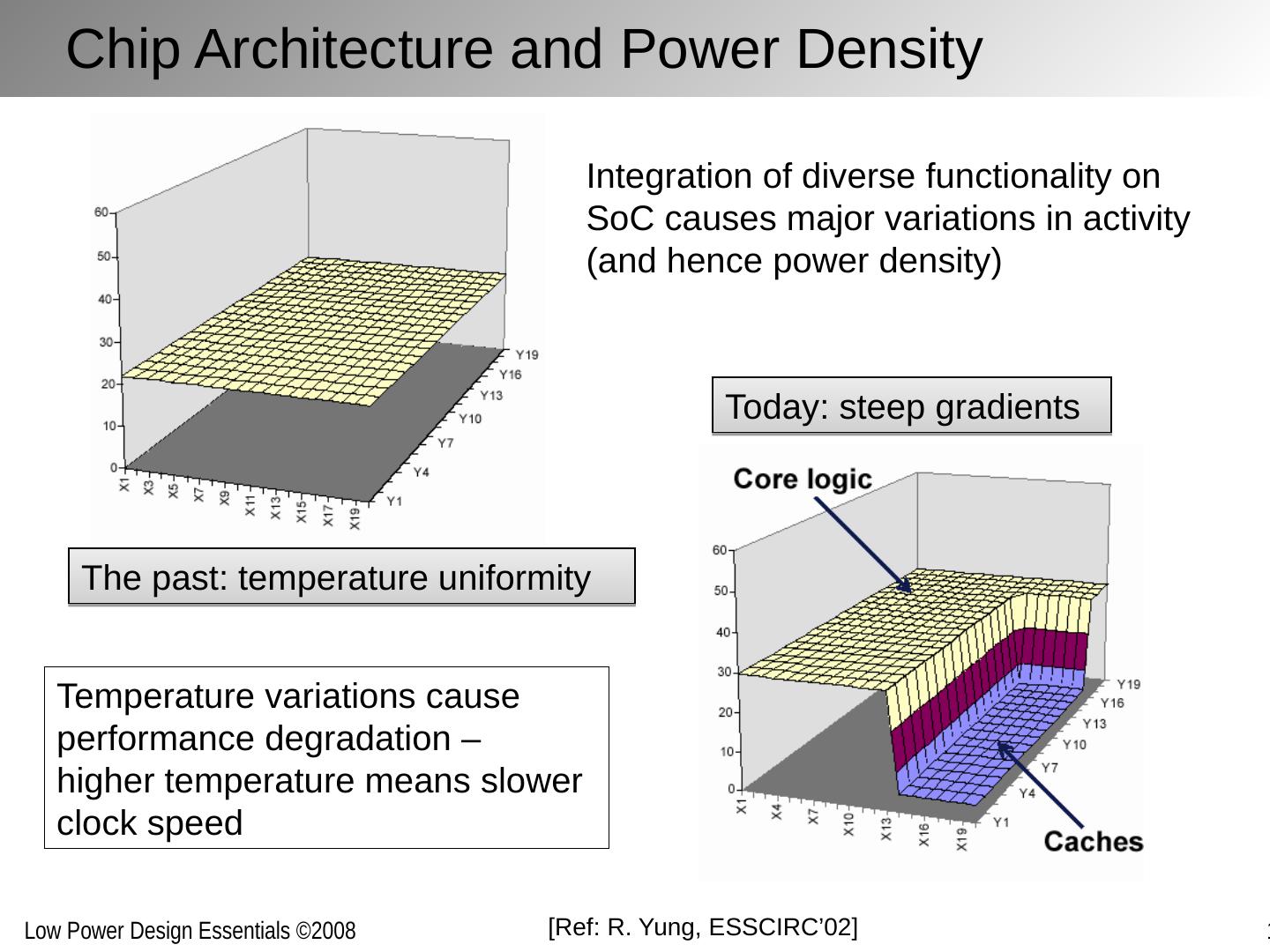

5 .Chip Architecture and Power Density [Ref: R. Yung, ESSCIRC’02 ] Integration of diverse functionality on SoC causes major variations in activity (and hence power density) The past: temperature uniformity Today: steep gradients Temperature variations cause performance degradation – higher temperature means slower clock speed

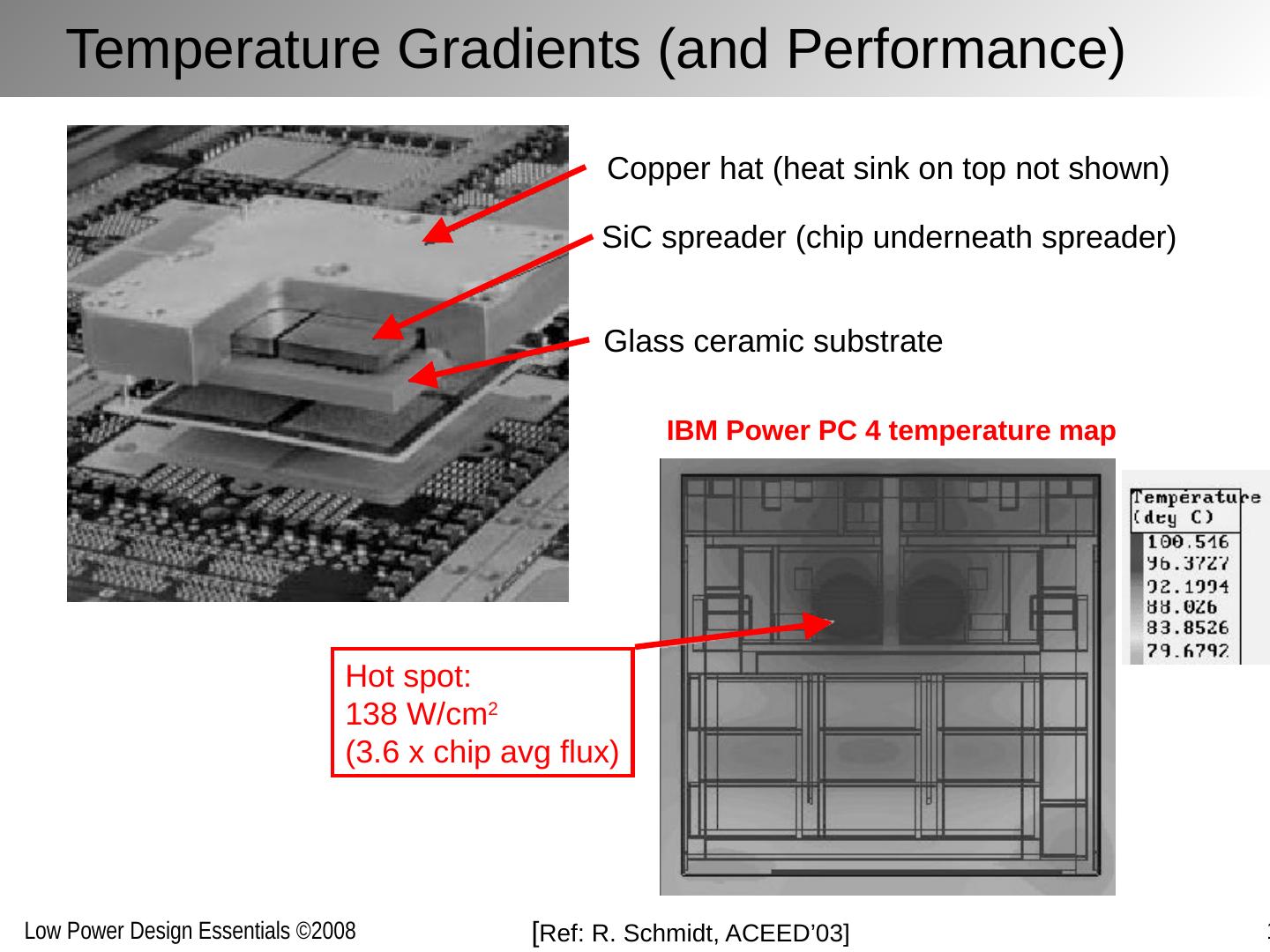

6 .Temperature Gradients (and Performance) IBM Power PC 4 temperature map [ Ref: R. Schmidt, ACEED’03] Hot spot: 138 W/cm 2 (3.6 x chip avg flux) Glass ceramic substrate SiC spreader (chip underneath spreader) Copper hat (heat sink on top not shown)

7 .Power the Dominant Design Constraint (2) Mobile Functionality Limited by Energy Budget [Ref: Y. Nuevo, ISSCC’04 ] Size of mobile sets energy supply Power consumption and Battery Capacity Trends © IEEE 2004

8 .Mobile Functionality Limited by Energy Budget [Ref: F. Snijders , Ambient Intelligence’05] Energy hierarchy in “ambient intelligent” environment © Springer 2005

9 .Battery Storage a Limiting Factor Basic technology has evolved little store energy using a chemical reaction Battery capacity increases between 3% and 7 % per year (doubled during the 90’s, relatively flat before that) Energy density/size, safe handling are limiting factor For extensive information on energy density of various materials, check http://en.wikipedia.org/wiki/Energy_density

10 .Battery Evolution Accelerated since the 1990’s, but slower than IC power growth.

11 .Battery Technology Saturating Battery capacity naturally plateaus as systems develop [Courtesy: M. Doyle , Dupont ]

12 .Need Higher Energy Density [Ref: R. Nowak, SECA’01] Fuel cells may increase stored energy more than a order of magnitude Example: Methanol = 5 kWh/kg Anode Electrolyte Cathode + ions Load e - + - Fuel 2H 2 4H + + 4e - Oxidant O 2 + 4H + + 4e - 2H 2 O H O

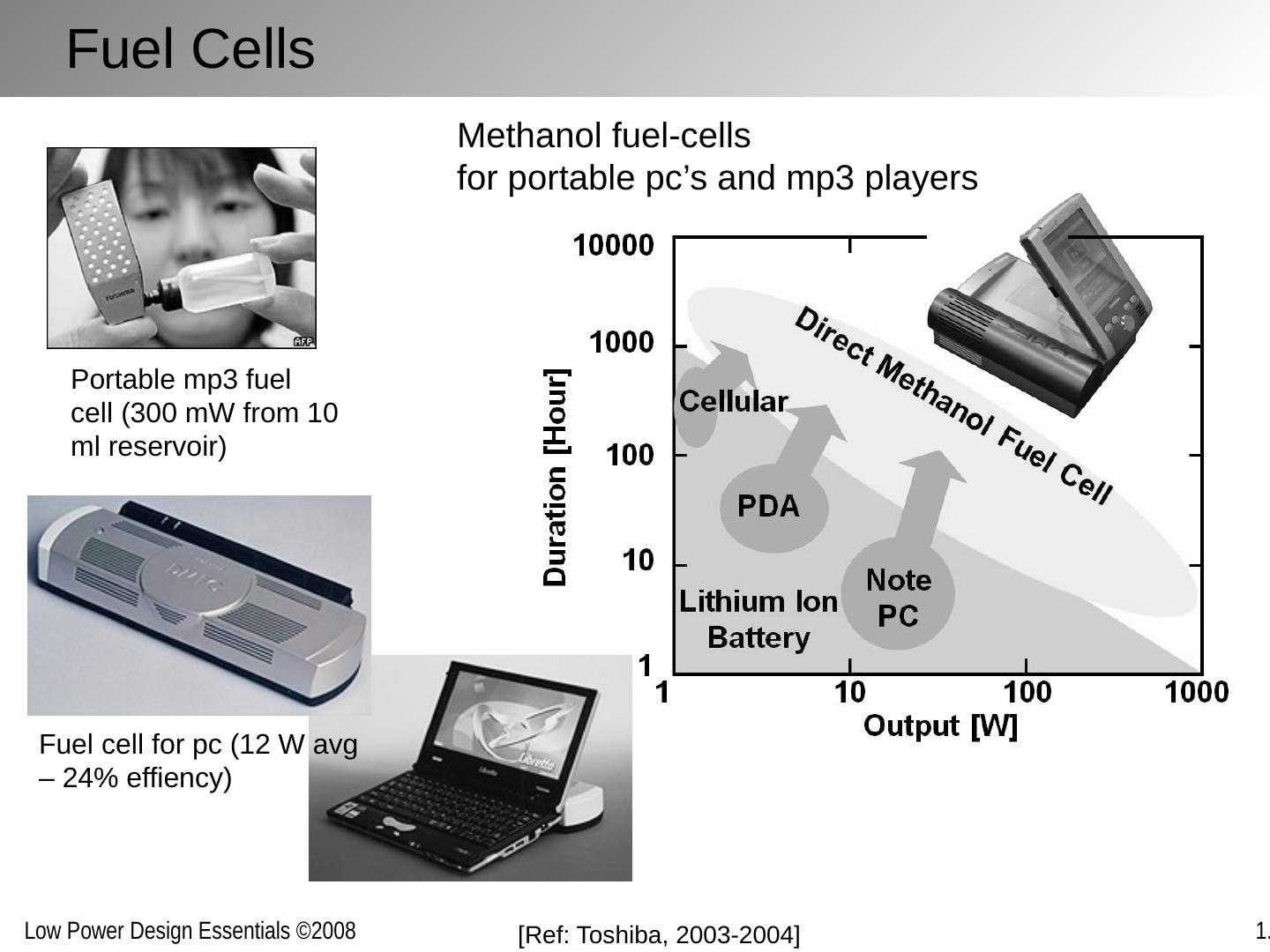

13 .Fuel Cells Methanol fuel-cells for portable pc’s and mp3 players [Ref: Toshiba, 2003-2004] Fuel cell for pc (12 W avg – 24% effiency) Portable mp3 fuel cell (300 mW from 10 ml reservoir)

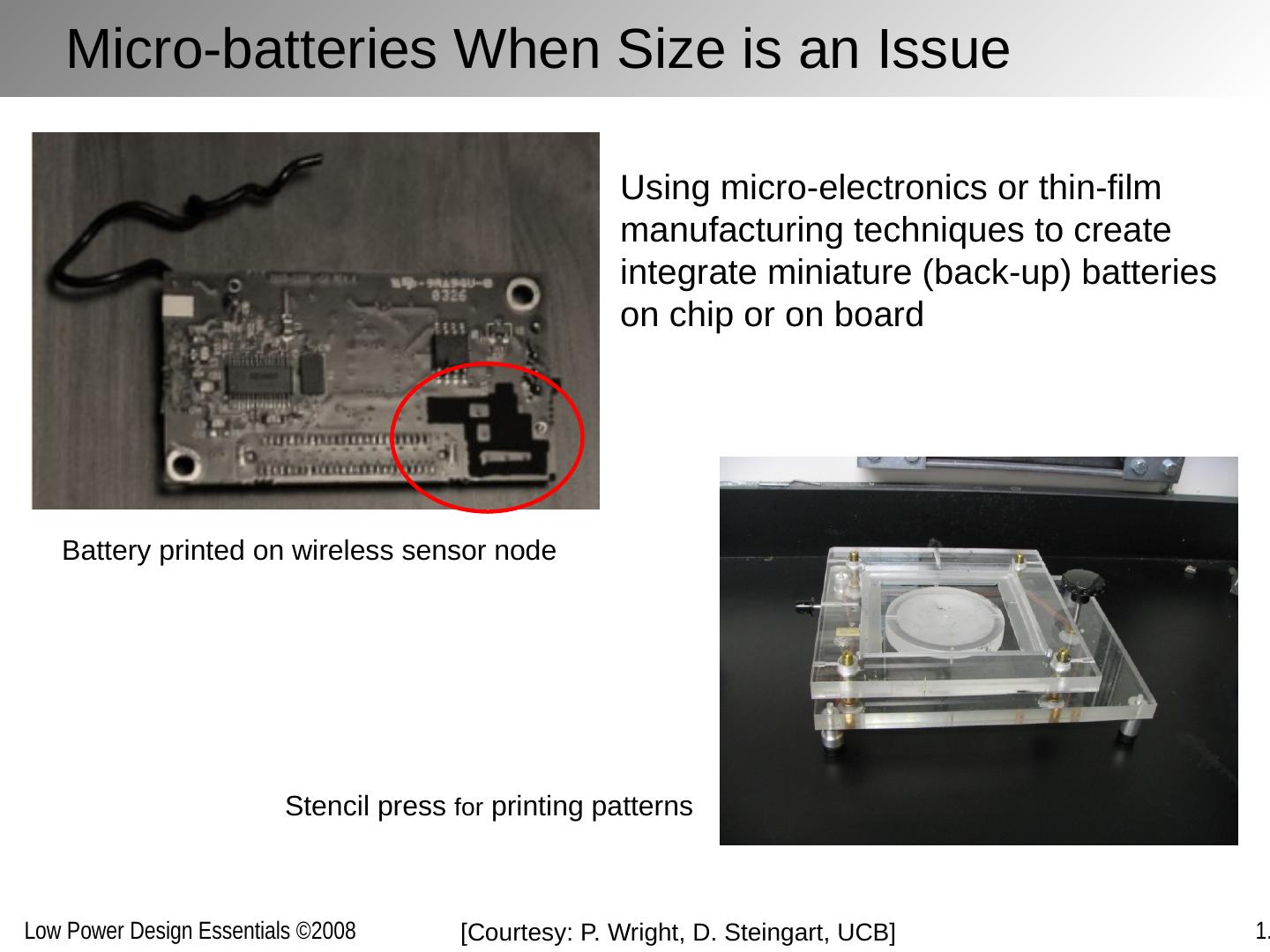

14 .Micro-batteries When Size is an Issue Battery printed on wireless sensor node Using micro-electronics or thin-film manufacturing techniques to create integrate miniature (back-up) batteries on chip or on board Stencil press for printing patterns [Courtesy: P. Wright, D. Steingart , UCB]

15 .How much Energy Storage in 1 cm 3 ? J/cm 3 m W/cm 3 /year Micro Fuel cell 3500 110 Primary battery 2880 90 Secondary battery 1080 34 Ultracapacitor 100 3.2 ultracapacitor Micro fuel cell ultracapacitor

16 .Power The Dominant Design Constraint (3) Exciting emerging applications require “zero-power ” Example: Computation/Communication Nodes for Wireless Sensor Networks Meso-scale low-cost wireless transceivers for ubiquitous wireless data acquisition that are fully integrated Size smaller than 1 cm 3 are dirt cheap At or below 1$ minimize power/energy dissipation Limiting power dissipation to 100 m W enables energy scavenging and form self-configuring, robust, ad-hoc networks containing 100’s to 1000’s of nodes [Ref: J. Rabaey, ISSCC’01]

17 .How to Make Electronics Truly Disappear? From 10’s of cm 3 and 10’s to 100’s of mW To 10’s of mm 3 and 10’s of m W

18 .Power the Dominant Design Constraint Exciting emerging applications require “zero-power” Real-time Health Monitoring Smart Surfaces Artificial Skin Philips Sand module UCB mm 3 radio UCB PicoCube Still at least one order of magnitude away

19 .How much Energy Can One Scavenge in 1 cm 3 ? m W /cm 3 Solar (outside) 15,000 Air flow 380 Human power 330 Vibration 200 Temperature 40 Pressure Var. 17 Solar (inside) 10 Thermal Air Flow Solar Vibrations

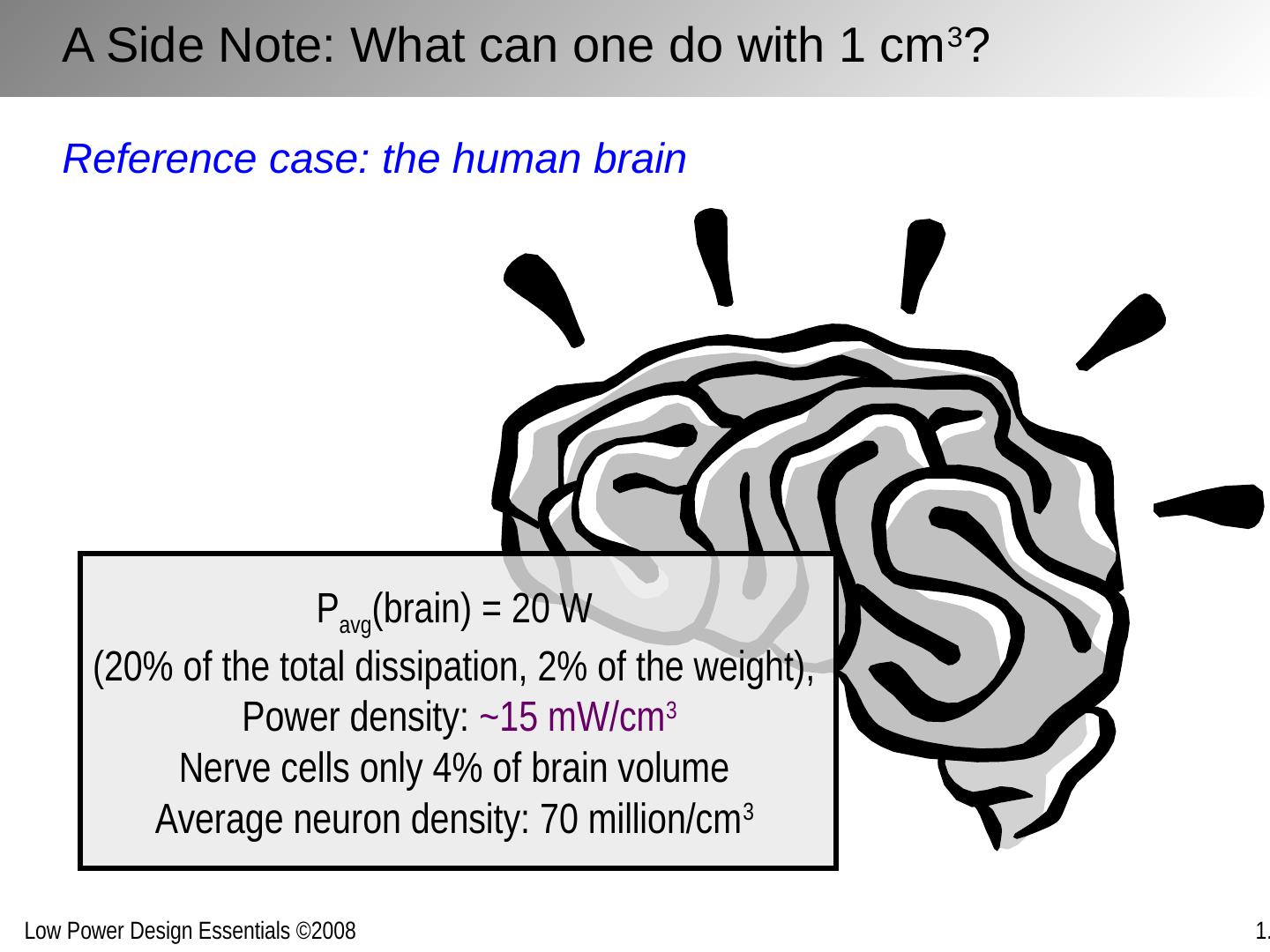

20 .A Side Note: What can one do with 1 cm 3 ? Reference case: the human brain P avg (brain) = 20 W (20% of the total dissipation, 2% of the weight), Power density: ~15 mW/cm 3 Nerve cells only 4% of brain volume Average neuron density: 70 million/cm 3

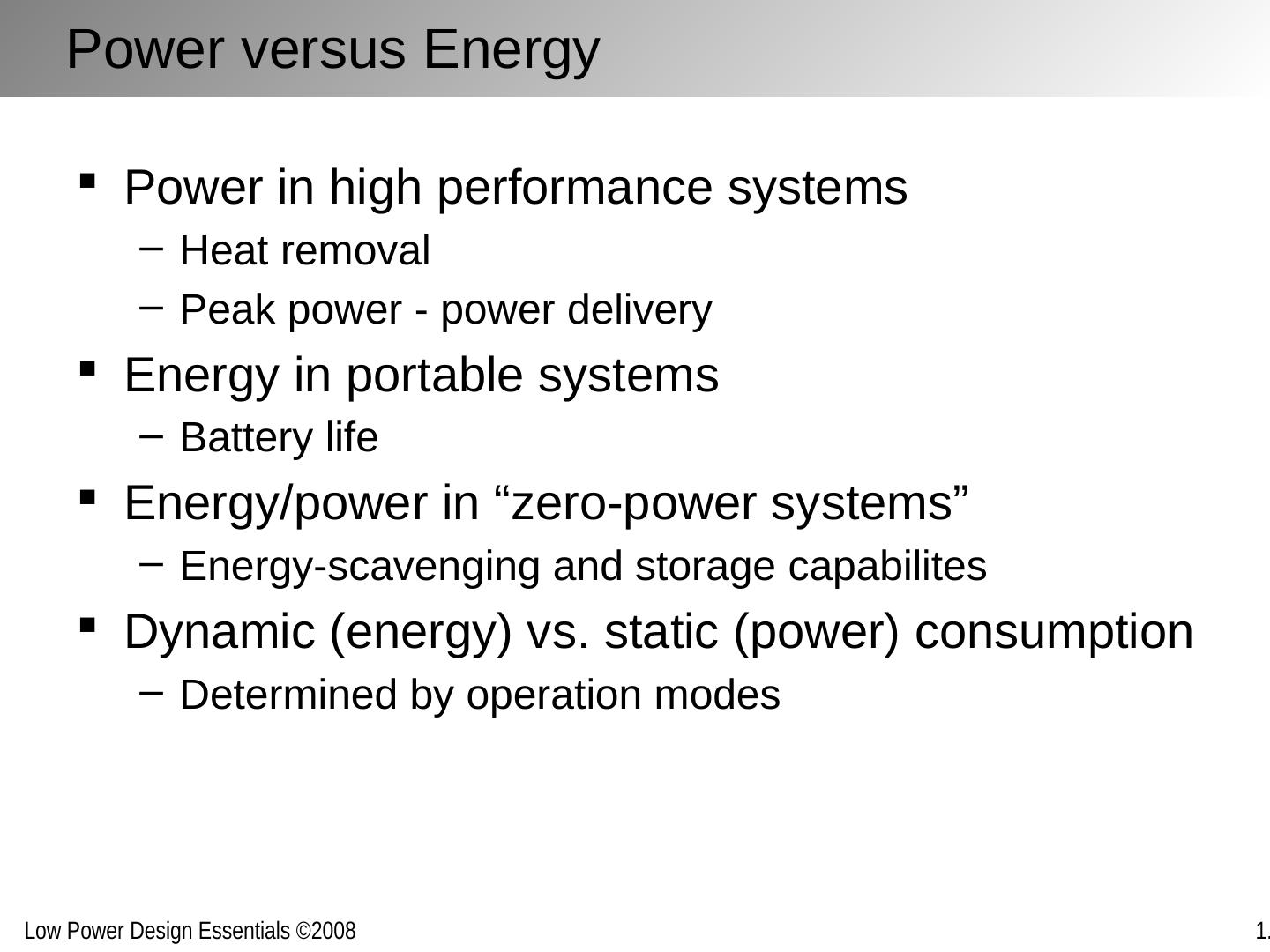

21 .Power versus Energy Power in high performance systems Heat removal Peak power - power delivery Energy in portable systems Battery life Energy/power in “zero-power systems” Energy-scavenging and storage capabilites Dynamic (energy) vs. static (power) consumption Determined by operation modes

22 .Power Evolution over Technology Generations Introduction of CMOS over bipolar bought industry 10 years (example: IBM mainframe processors) [Ref: R. Chu, JEP’04] Year of Announcement 1950 1960 1970 1980 1990 2000 2010 Module Heat Flux(watts/cm 2 ) 0 2 4 6 8 10 12 14 Bipolar CMOS Vacuum IBM 360 IBM 370 IBM 3033 IBM ES9000 Fujitsu VP2000 IBM 3090S NTT Fujitsu M-780 IBM 3090 CDC Cyber 205 IBM 4381 IBM 3081 Fujitsu M380 IBM RY5 IBM GP IBM RY6 Apache Pulsar Merced IBM RY7 IBM RY4 Pentium II(DSIP) T-Rex Squadrons Pentium 4 Mckinley Start of Water Cooling Prescott Jayhawk(dual) © ASME 2004

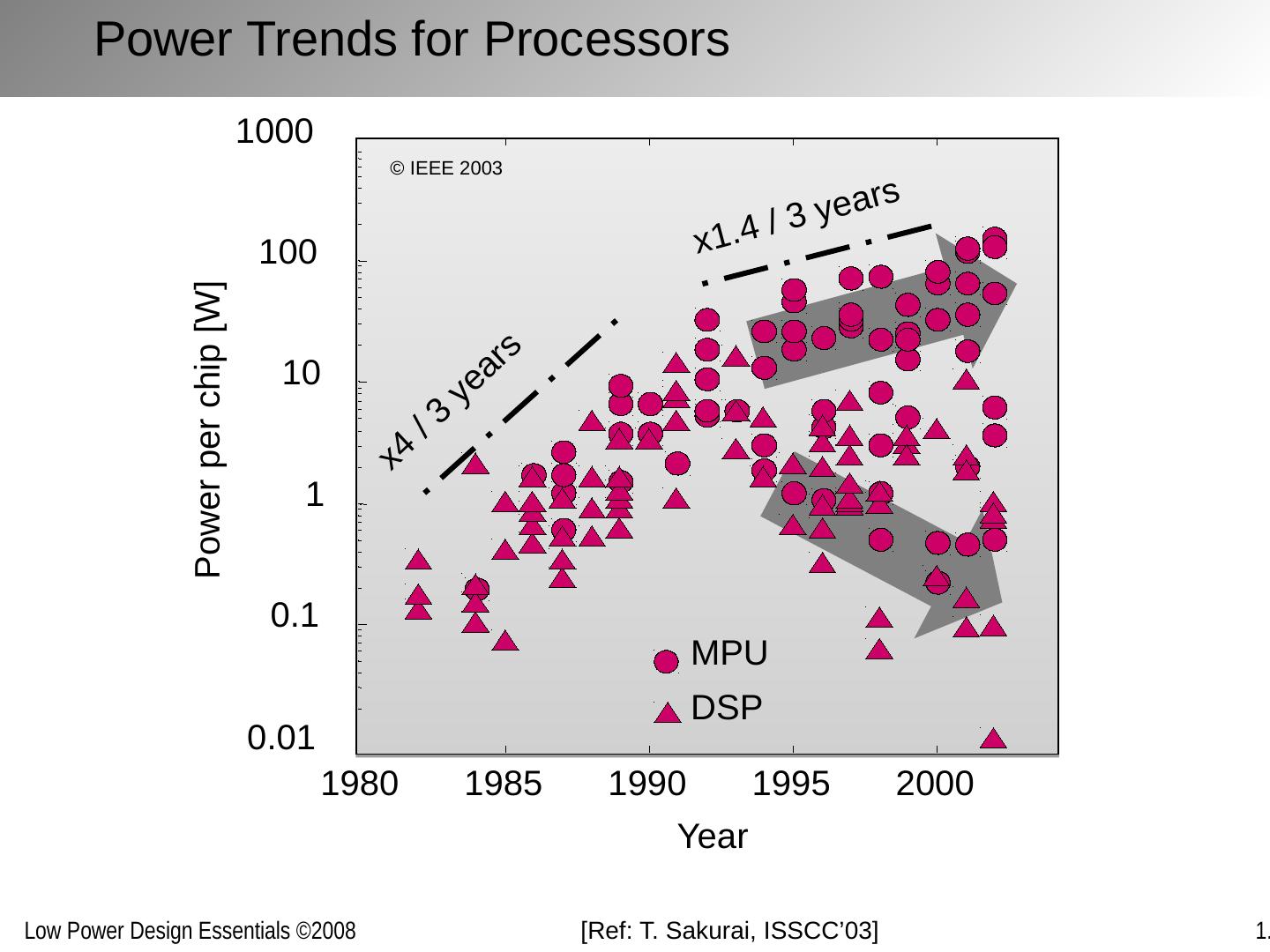

23 .Power Trends for Processors [Ref: T. Sakurai, ISSCC’03] Power per chip [W] 1980 1985 1990 1995 2000 0.01 0.1 1 10 100 1000 Year MPU x4 / 3 years DSP x1.4 / 3 years © IEEE 2003

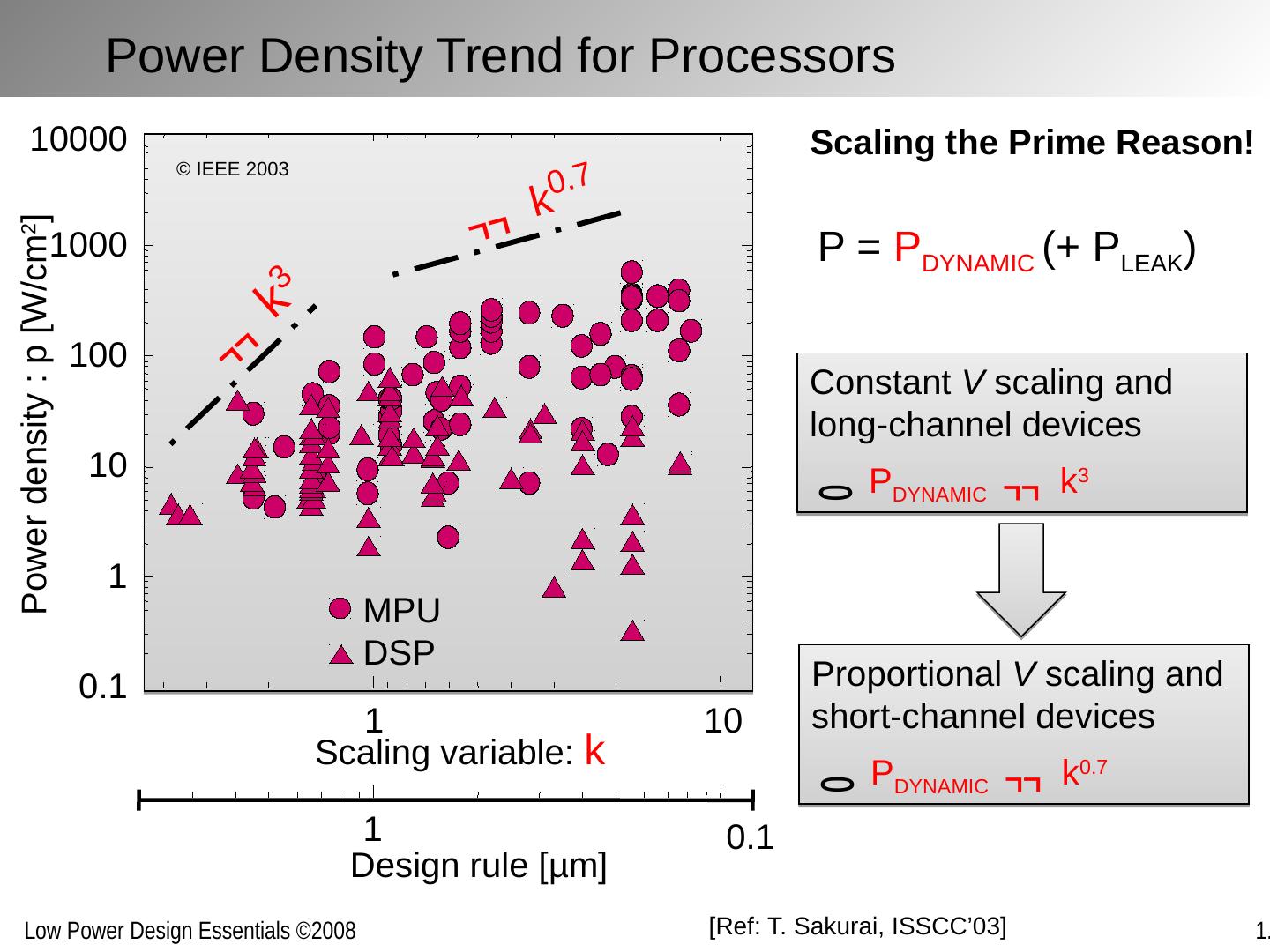

24 .Power Density Trend for Processors P = P DYNAMIC (+ P LEAK ) [Ref: T. Sakurai, ISSCC’03 ] Scaling the Prime Reason! Power density : p [W/cm 2 ] 0.1 1 10 100 1000 1 10 Design rule [ µ m] 0.1 1 Scaling variable: k k 3 10000 k 0.7 MPU DSP Constant V scaling and long-channel devices P DYNAMIC k 3 Proportional V scaling and short-channel devices P DYNAMIC k 0.7 © IEEE 2003

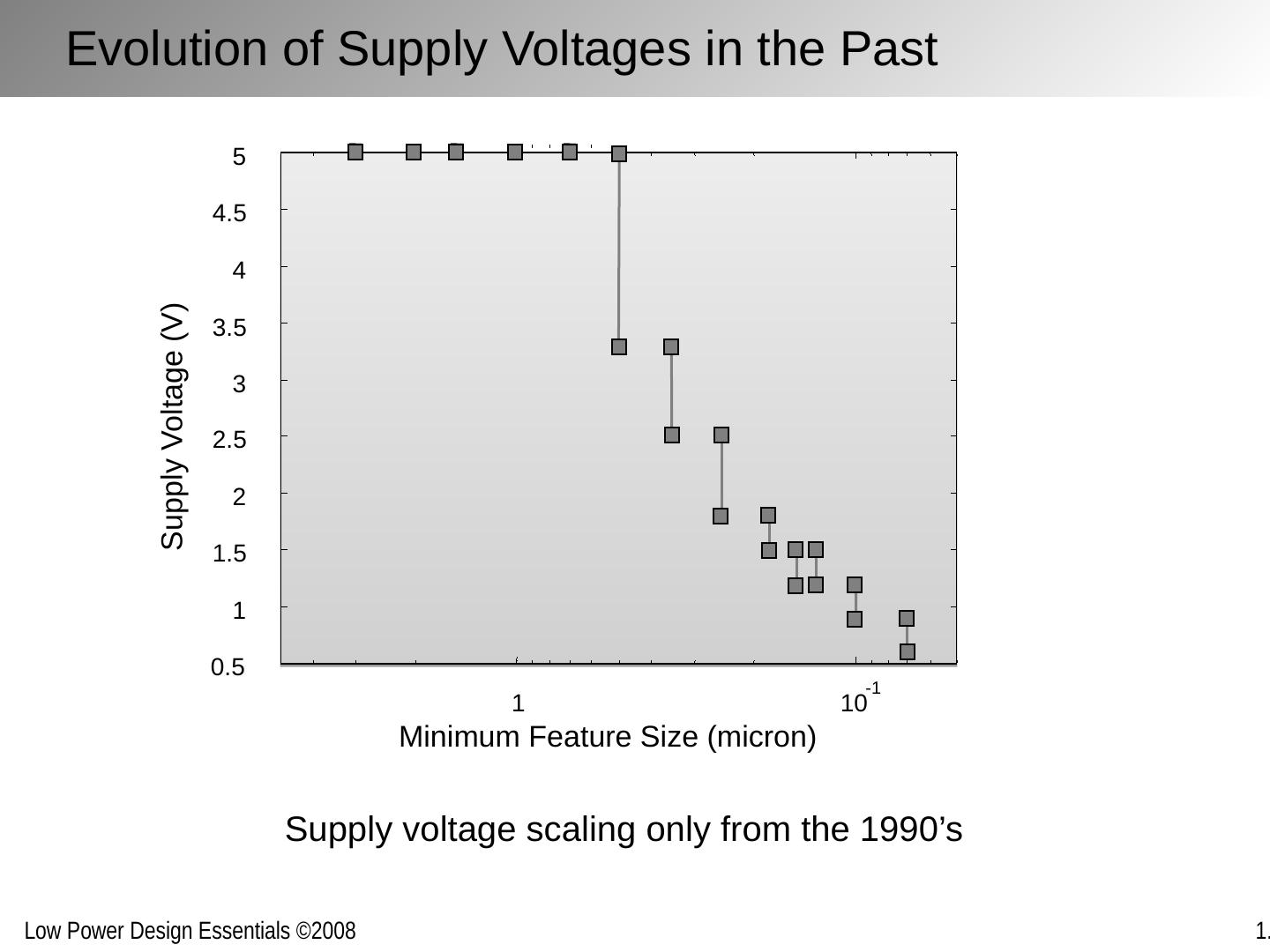

25 .Evolution of Supply Voltages in the Past Minimum Feature Size (micron) 10 -1 1 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5 Supply Voltage (V) Supply voltage scaling only from the 1990’s

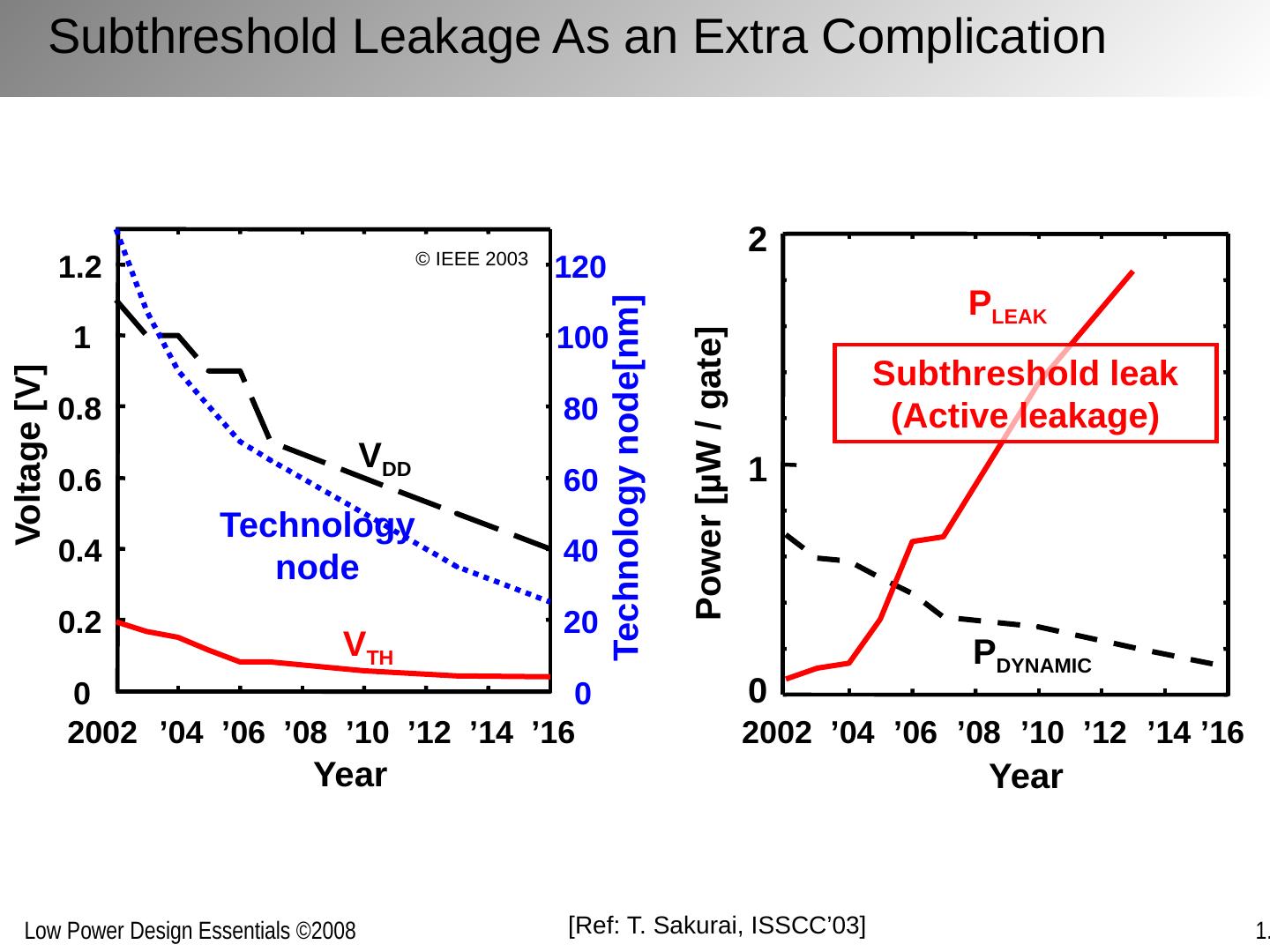

26 . Subthreshold Leakage As an Extra Complication Year 2002 ’04 ’06 ’08 ’10 ’12 ’14 ’16 0 0.2 0.4 0.6 0.8 1 1.2 0 20 40 60 80 100 120 Technology node[nm] Voltage [V] V TH V DD Technology node 2002 ’04 ’06 ’08 ’10 ’12 ’14 ’16 0 1 2 Year P DYNAMIC P LEAK Power [ µ W / gate] Subthreshold leak (Active leakage) [Ref: T. Sakurai, ISSCC’03 ] © IEEE 2003

27 .Static Power (Leakage) may Ruin Moore ’ s Law Power per chip [W] 1980 1985 1990 1995 2000 0.01 0.1 1 10 100 1000 Year MPU x4 / 3 years DSP x1.4 / 3 years Processors published in ISSCC 2005 2010 2015 x1.1 / 3 years ITRS requirement 10000 Dynamic Leakage 1/100 [Ref: T. Sakurai, ISSCC 03] © IEEE 2003

28 .Power Density Increases [Courtesy: S. Borkar , Intel] 4004 8008 8080 8085 8086 286 386 486 Pentium ® proc P6 1 10 100 1000 10000 1970 1980 1990 2000 2010 Year Power Density (W/cm2) Hot Plate Nuclear Reactor Rocket Nozzle Sun’s Surface Upper Bound? Unsustainable in the long term

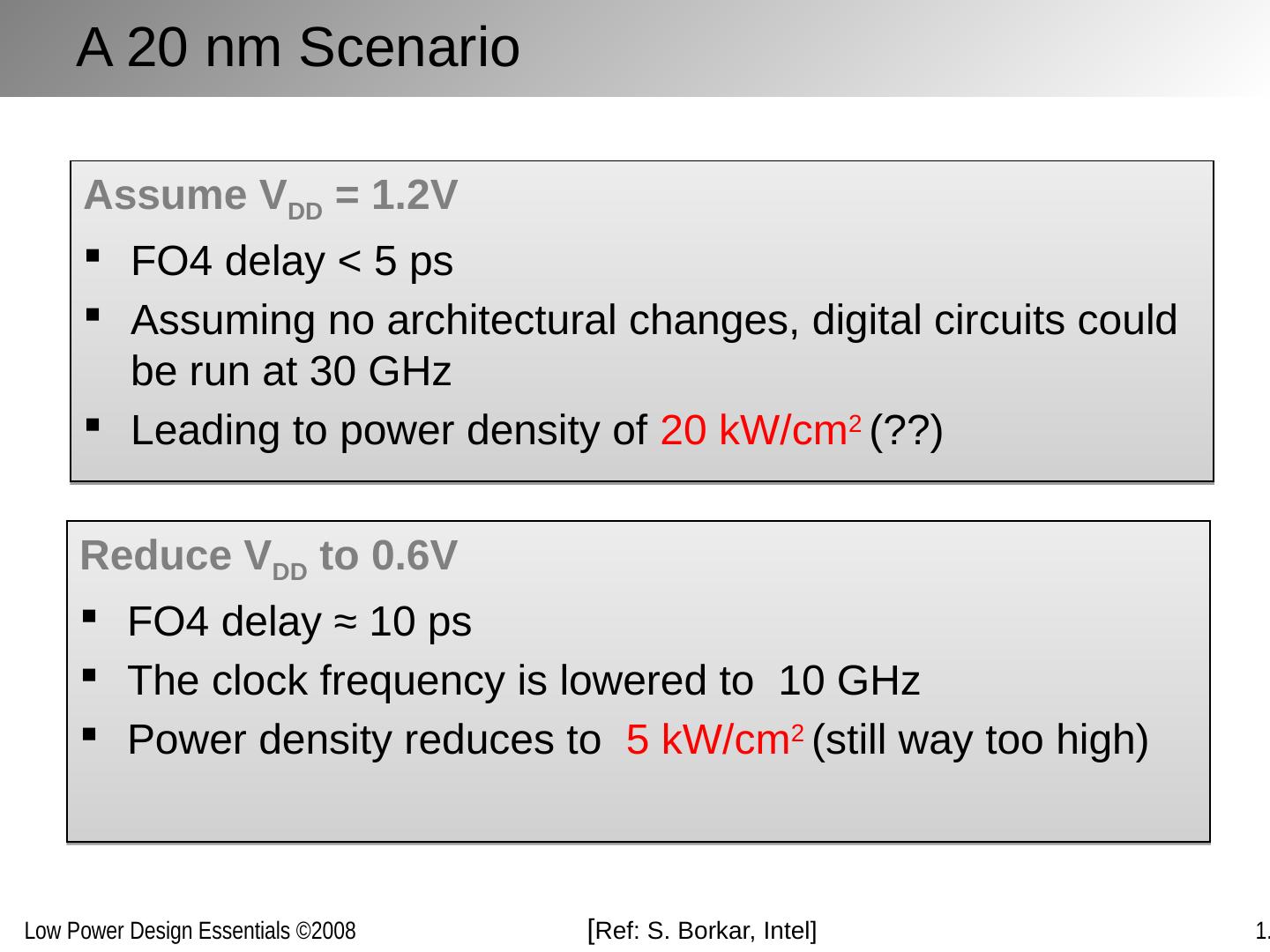

29 .Projecting Into the Future 2003 ITRS – Low operating power scenario Active power density: k 1.9 Leakage power density: k 2.7 Compute density: k 3 2005 ITRS – Low operating power scenario FD-SOI Dual Gate Power density (active and static) accelerating anew. Technology innovations help, but impact limited.