- 快召唤伙伴们来围观吧

- 微博 QQ QQ空间 贴吧

- 文档嵌入链接

- <iframe src="https://www.slidestalk.com/u20/mcs51_sdkzjs?embed" frame border="0" width="640" height="360" scrolling="no" allowfullscreen="true">复制

- 微信扫一扫分享

MCS51 - 计算机原理与应用

展开查看详情

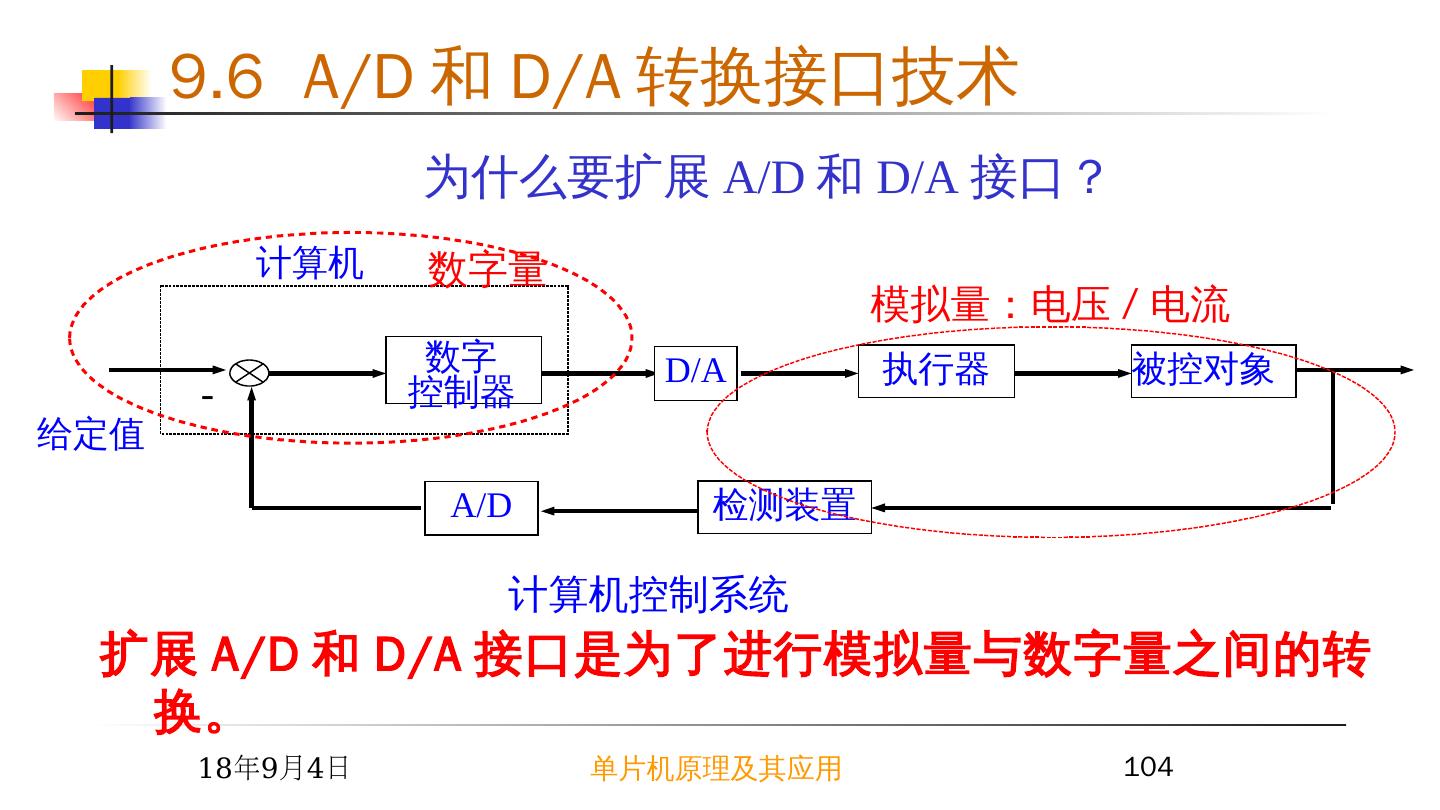

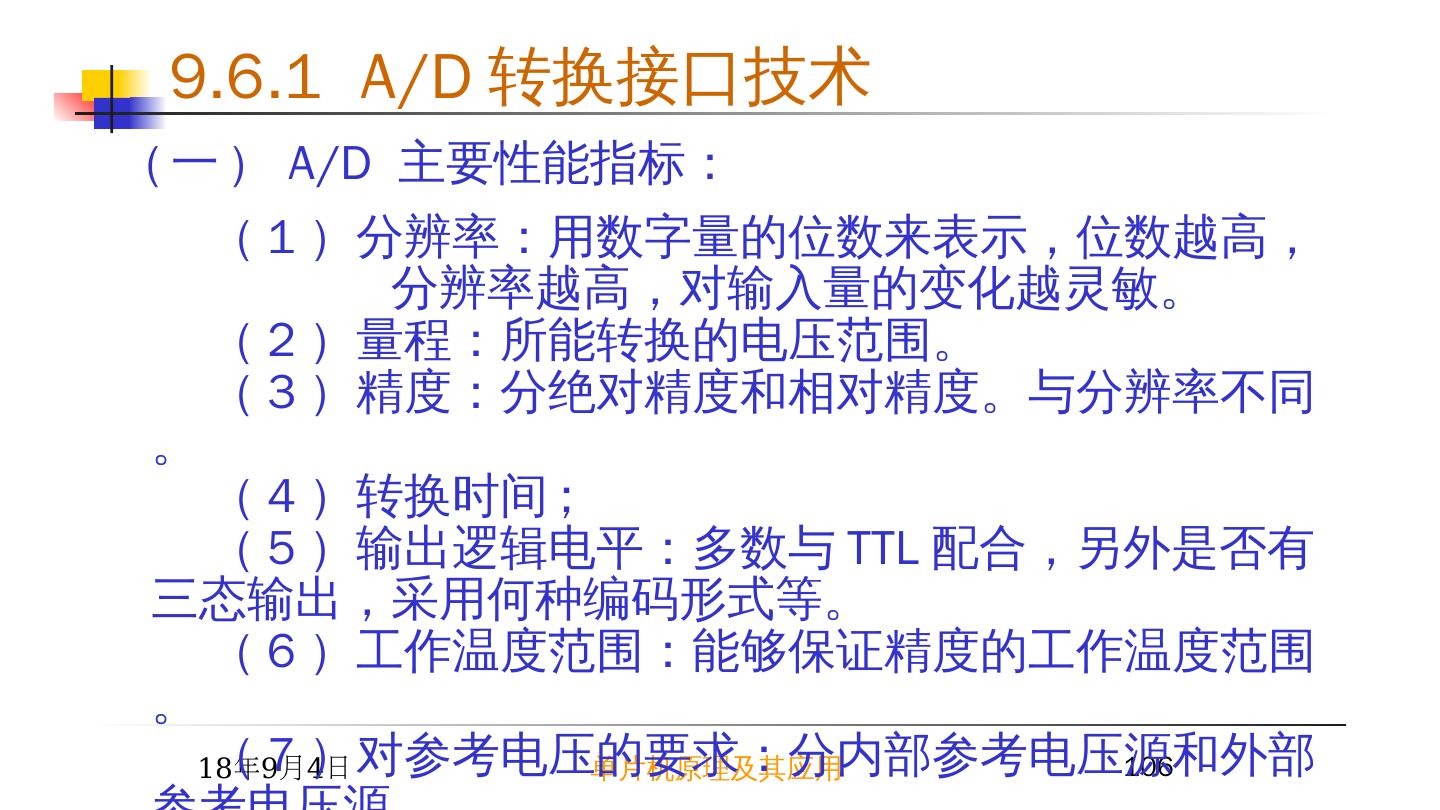

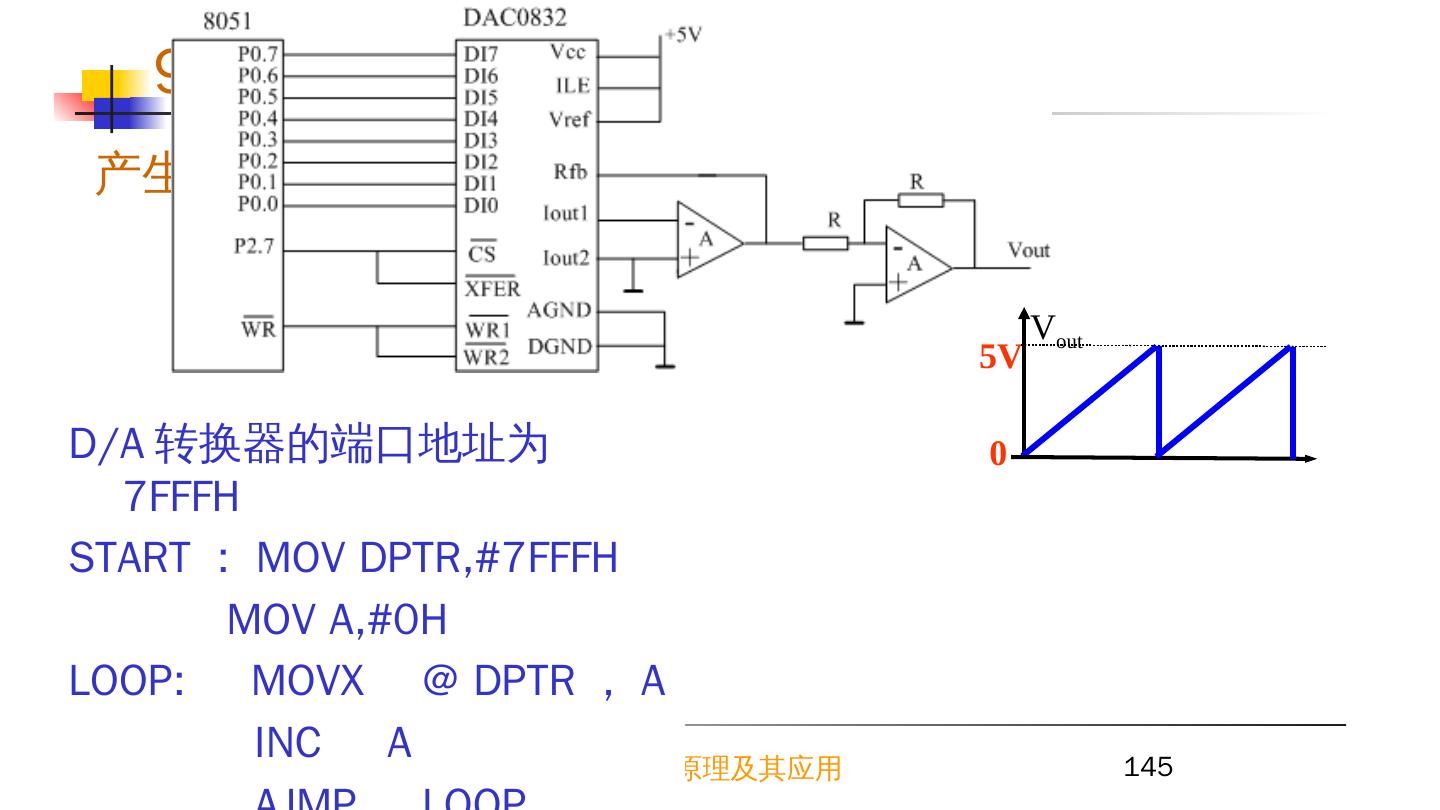

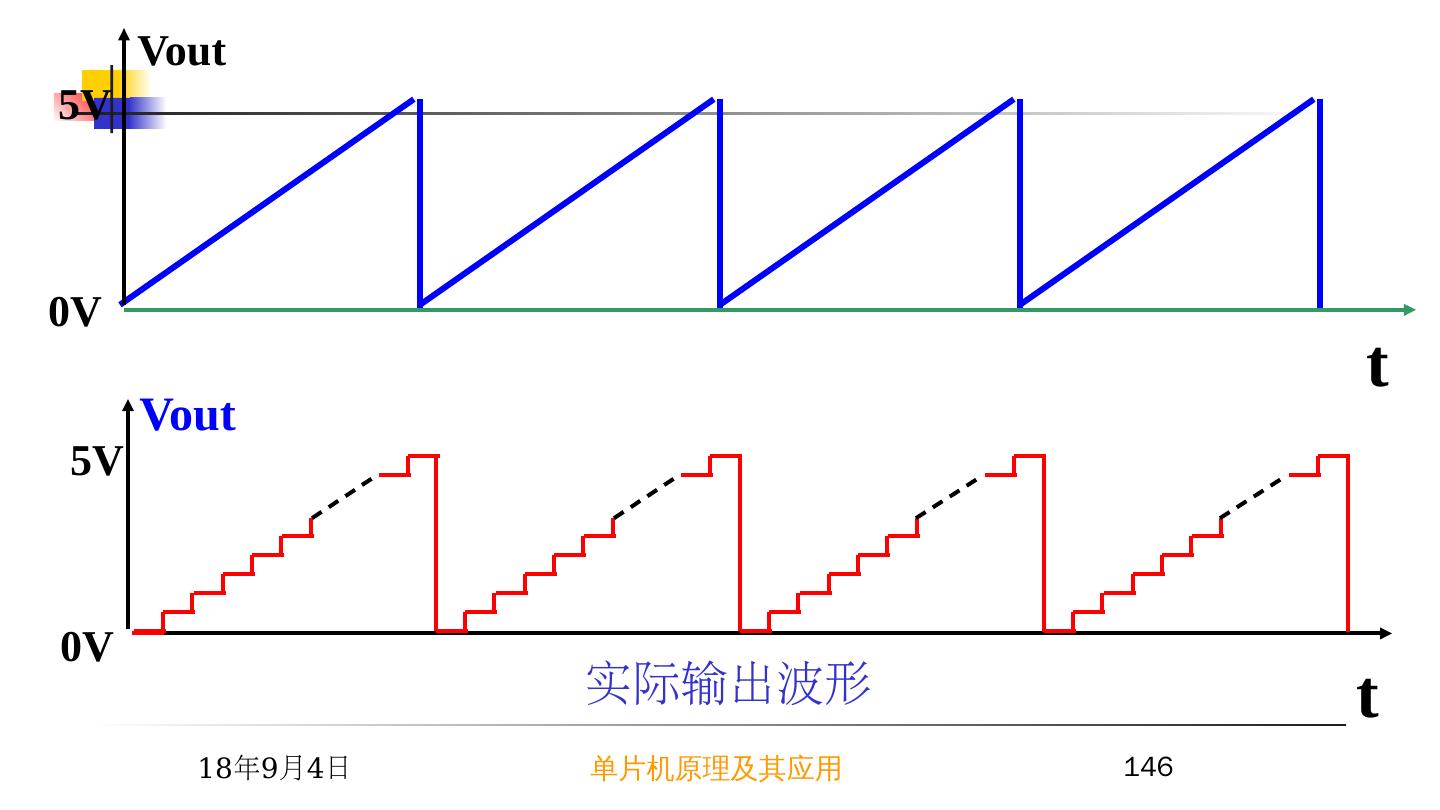

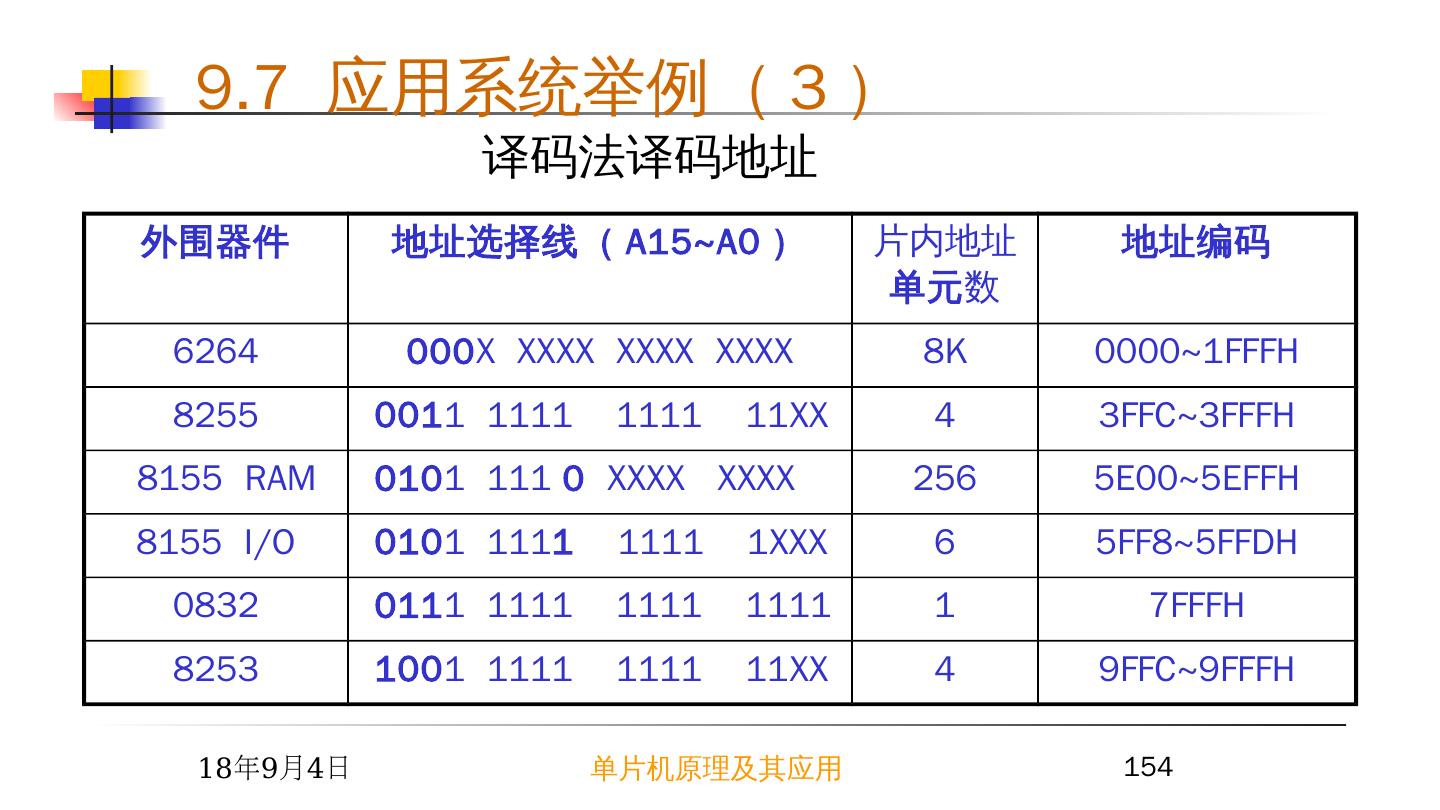

1 .第 9 章单片机 I/O 接口扩展技术 简单芯片扩展 I/O 接口 8155 可编程接口芯片及其使用 键盘及显示器接口设计 A/D 和 D/A 转换接口技术 主 要 内 容

2 .2015/6/23 单片机原理及其应用 2 9.1 I/O 接口概述 —— I/O 接口的功能 1 I/O 接口的功能 速度匹配:锁存数据、传送联络信号。输入设备数据缓冲适应 CPU 的快速操作。 数据格式转换:并 - 串转换、 A/D 、 D/A 转换。 电平转换:电平幅值或正 / 负逻辑转换。 隔离:通过接口三态门将总线与其它设备隔离。

3 .2015/6/23 单片机原理及其应用 3 9.1 I/O 接口概述 —— I/O 接口的功能 2 I/O 接口的编址方式 存储器统一编址方式: CPU 将 I/O 接口当作存储单元对待,访问 I/O 与访问存储器单元操作相同 I/O 独立编址方式: 另外设立一个独立的 I/O 空间,与存储器空间互不影响,单独编址供 I/O 设备使用。 在指令系统中,有专用于 I/O 访问的指令。

4 .2015/6/23 单片机原理及其应用 4 3 I/O 接口 数据传送方式 外设 READY ? Y N 数据传送 读接口状态 同步传送方式(无条件传送) 外设 与 CPU 速度相当时,采用此种方式。如: 单片机 与 外部 RAM 之间的数据传送。 查询传送方式(条件传送) CPU 与 I/O 接口之间的数据传送由程序控制来实现。通过查询外设是否准备就绪来决定是否传送数据。 通用性好 , 软硬件简单 ,CPU 效率低。 9.1 I/O 接口概述 —— I/O 接口的功能

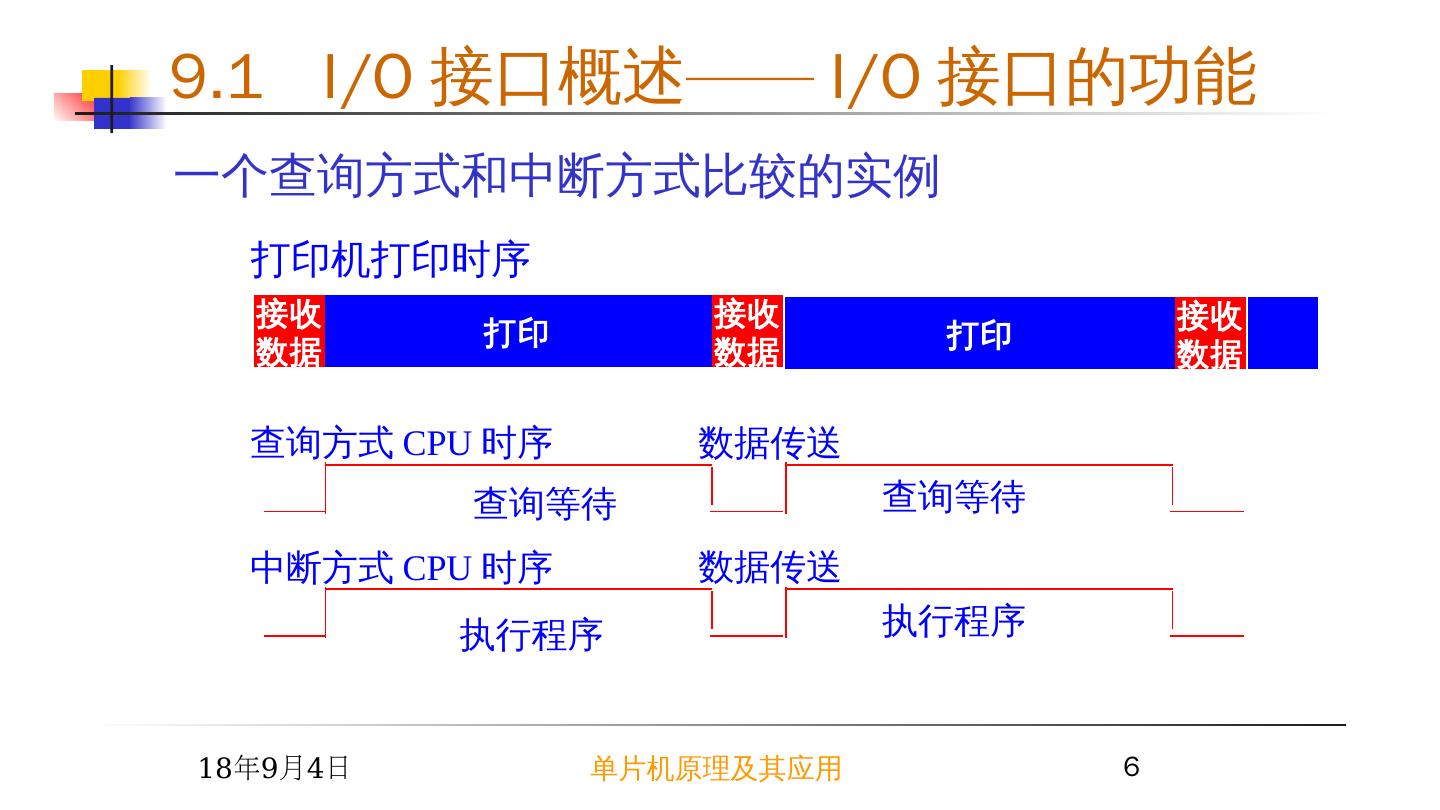

5 .2015/6/23 单片机原理及其应用 5 中断控制传送方式 ( 1 )任何外设与 CPU 交换信息,需向 CPU 发出中断申请; ( 2 ) CPU 检测到中断请求,若满足中断响应条件, CPU 立即停止正在执行的程序,转去执行中断处理程序 , 进行数据传送。 ( 3 )中断处理完毕返回被中断的程序处,继续执行原来的程序。 CPU 的效率提高。 9.1 I/O 接口概述 —— I/O 接口的功能

6 .2015/6/23 单片机原理及其应用 6 打印 接收 数据 打印 接收 数据 接收 数据 打印机打印时序 查询方式 CPU 时序 查询等待 数据传送 查询等待 中断方式 CPU 时序 执行程序 数据传送 执行程序 一个查询方式和中断方式比较的实例 9.1 I/O 接口概述 —— I/O 接口的功能

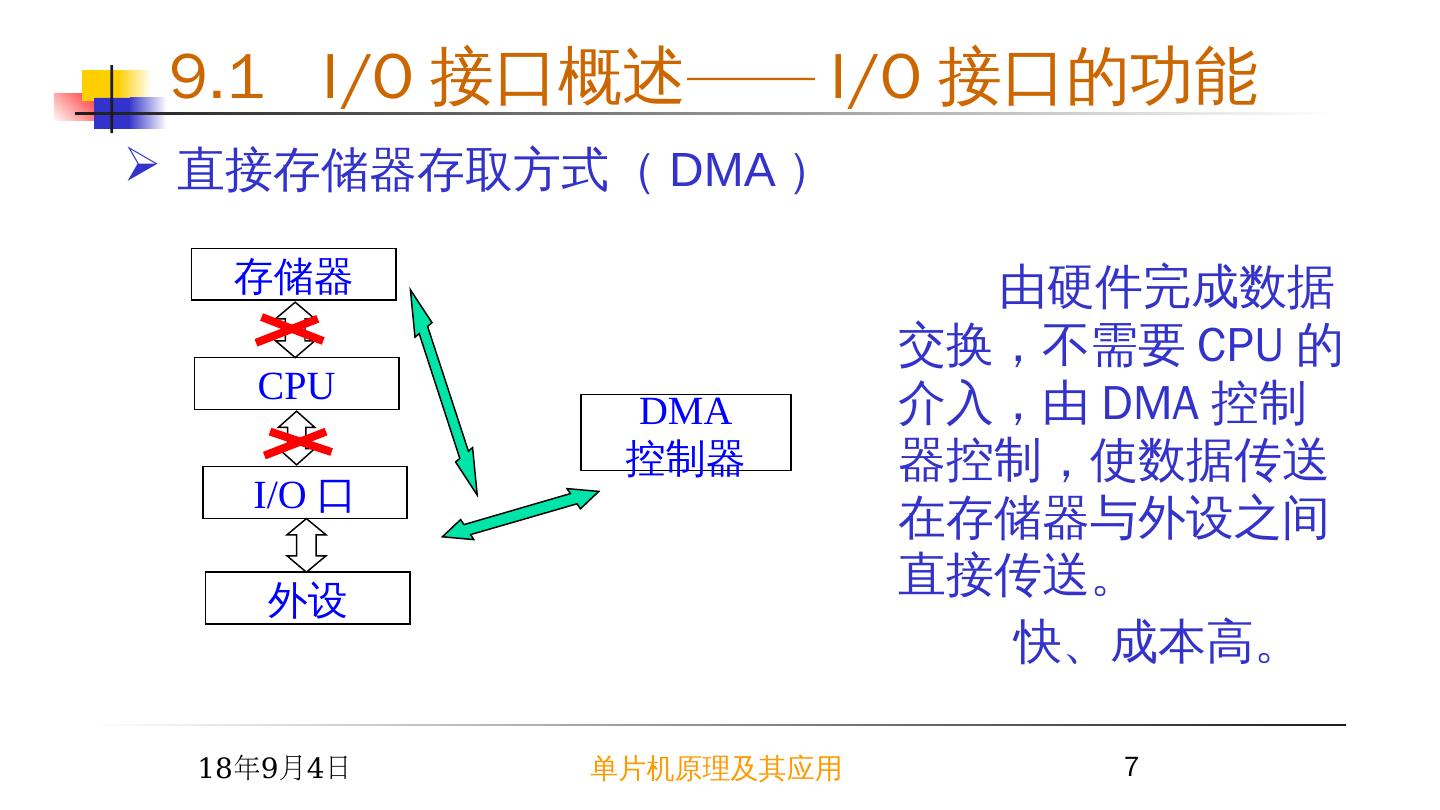

7 .2015/6/23 单片机原理及其应用 7 由硬件完成数据交换,不需要 CPU 的介入,由 DMA 控制器控制,使数据传送在存储器与外设之间直接传送。 快、成本高。 存储器 CPU 外设 I/O 口 DMA 控制器 直接存储器存取方式 ( DMA ) 9.1 I/O 接口概述 —— I/O 接口的功能

8 .2015/6/23 单片机原理及其应用 8 MCS - 51 系列单片机的外部 RAM 和 I/O 口是统一编址的,因此用户可以把单片机外部 64KRAM 空间的一部分作为扩展 I/O 的地址空间。 单片机可以像访问外部 RAM 存储器那样访问外部接口芯片,对其口进行读写操作,在逻辑操作和指令使用上无任何区别。 4 MCS-51 单片机的 I/O 接口扩展 9.1 I/O 接口概述 —— I/O 接口的功能

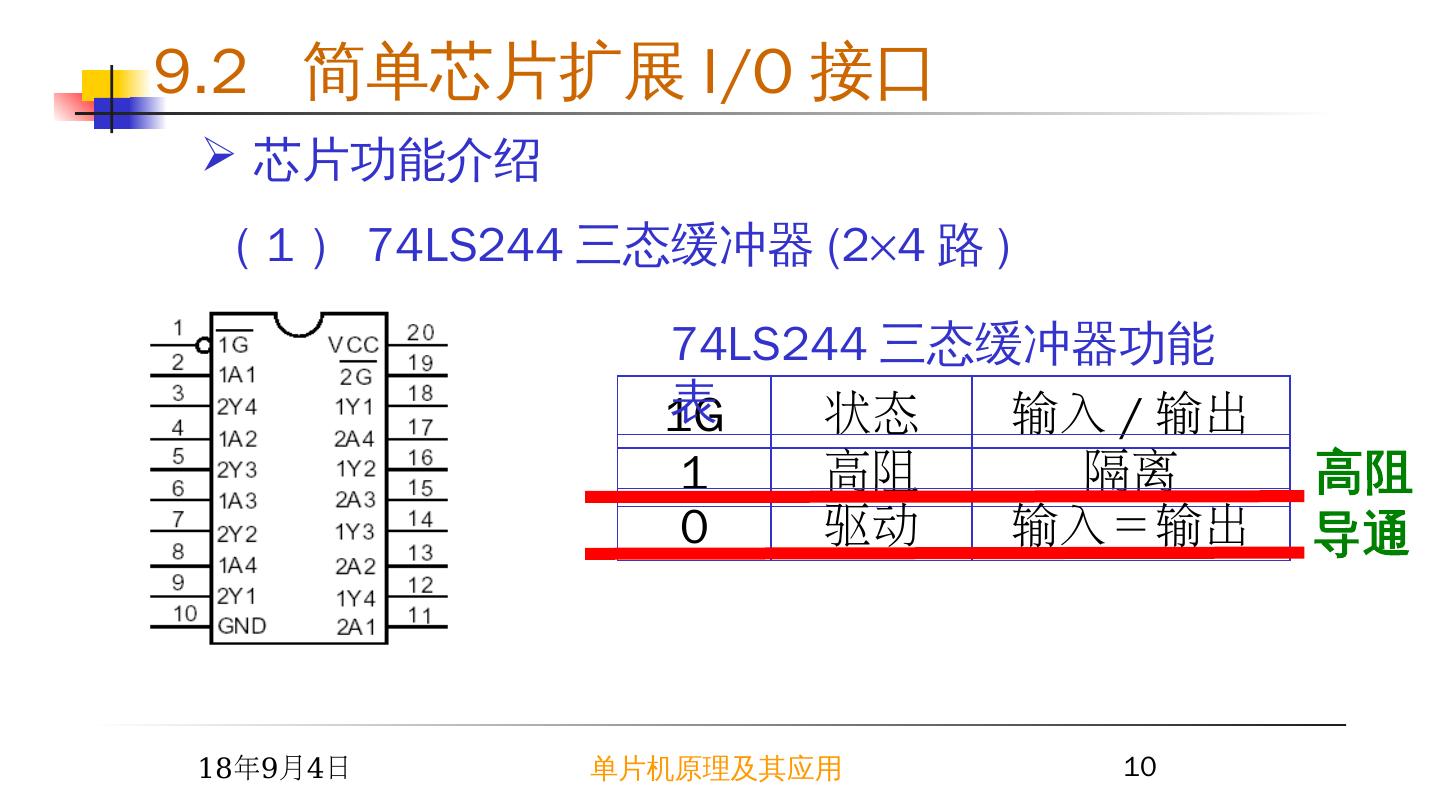

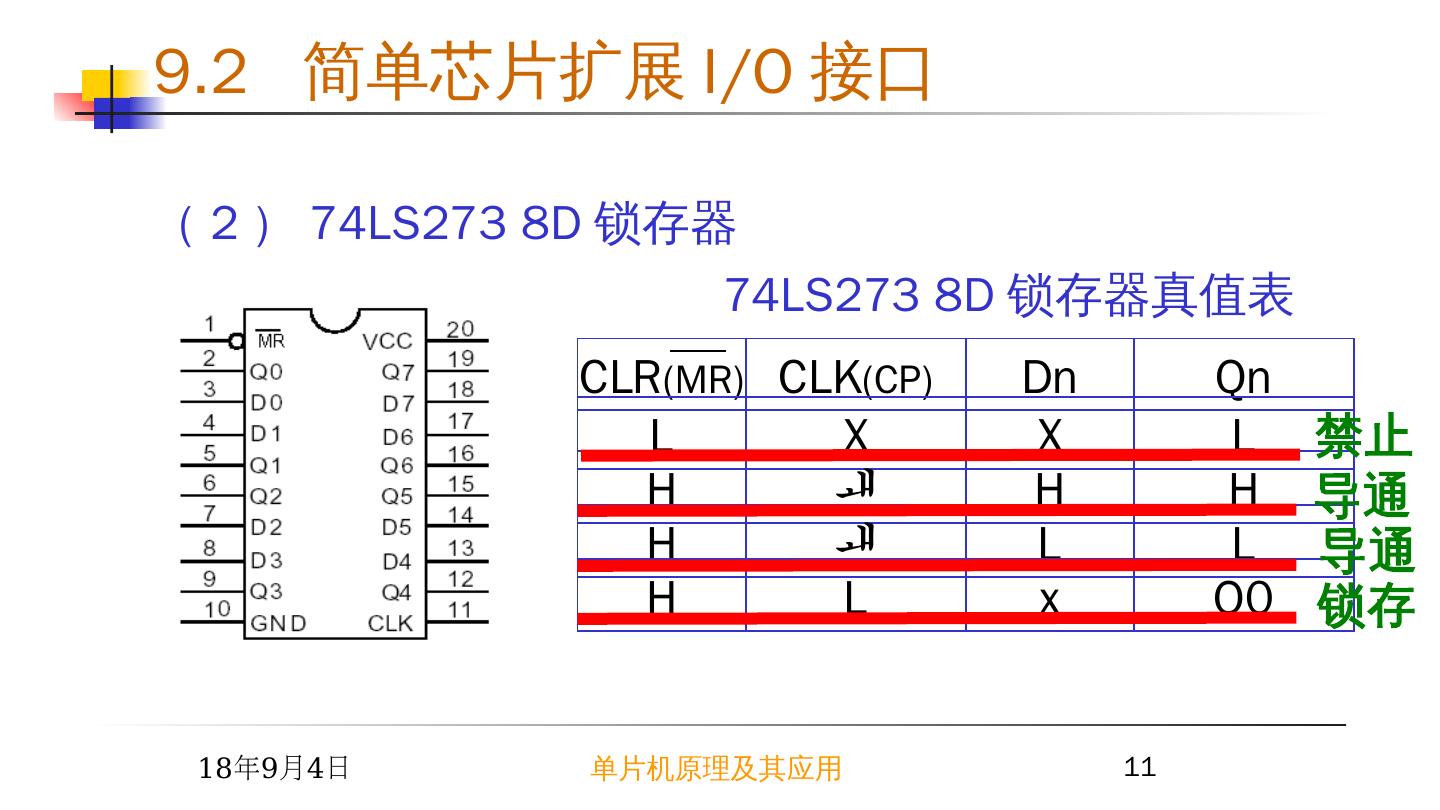

9 .2015/6/23 单片机原理及其应用 9 实现方式 采用 TTL 、 CMOS 电路。 设计原则 输入口具有缓冲作用 —— 缓冲器。 输出口具有锁存作用 —— 锁存器。 常用 TTL 芯片 缓冲器 : 74LS244 , 74LS245 锁存器: 74LS273 , 74LS373 , 74LS374 , 74LS377 等。 9.2 简单芯片扩展 I/O 接口

10 .2015/6/23 单片机原理及其应用 10 芯片功能介绍 ( 1 ) 74LS244 三态缓冲器 (2 4 路 ) 1G 状态 输入 / 输出 1 高阻 隔离 0 驱动 输入=输出 74LS244 三态缓冲器功能表 9.2 简单芯片扩展 I/O 接口 高阻 导通

11 .2015/6/23 单片机原理及其应用 11 CLR (MR) CLK (CP) L X H Dn Qn X L H H H H L L L x Q0 74LS273 8D 锁存器真值表 ( 2 ) 74LS273 8D 锁存器 9.2 简单芯片扩展 I/O 接口 禁止 导通 导通 锁存

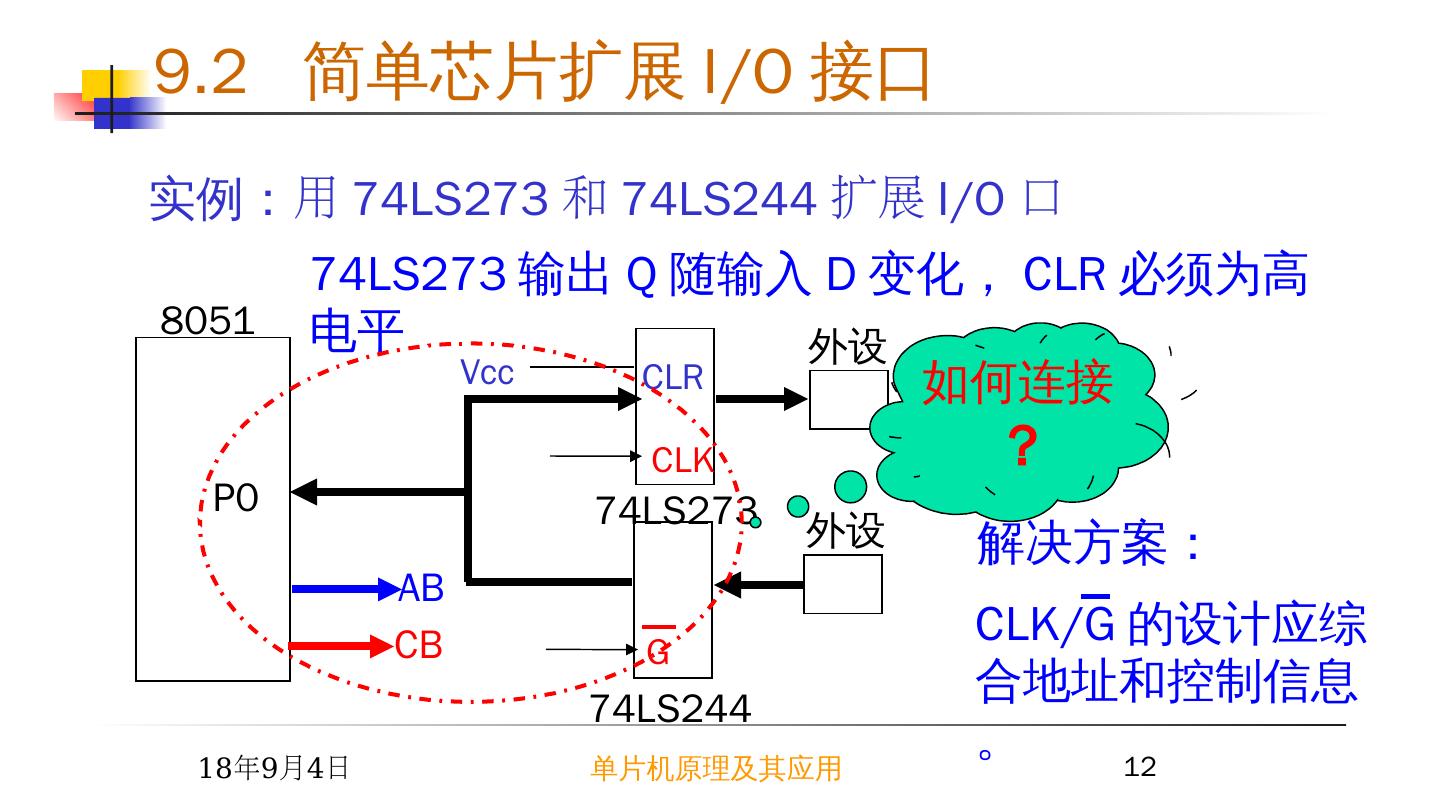

12 .2015/6/23 单片机原理及其应用 12 外设 外设 74LS273 74LS244 8051 P0 CLK G AB CB CLR Vcc 74LS273 输出 Q 随输入 D 变化, CLR 必须为高电平 如何连接 ? CLK/G 的设计应综合地址和控制信息。 解决方案: 实例 : 用 74LS273 和 74LS244 扩展 I/O 口 9.2 简单芯片扩展 I/O 接口

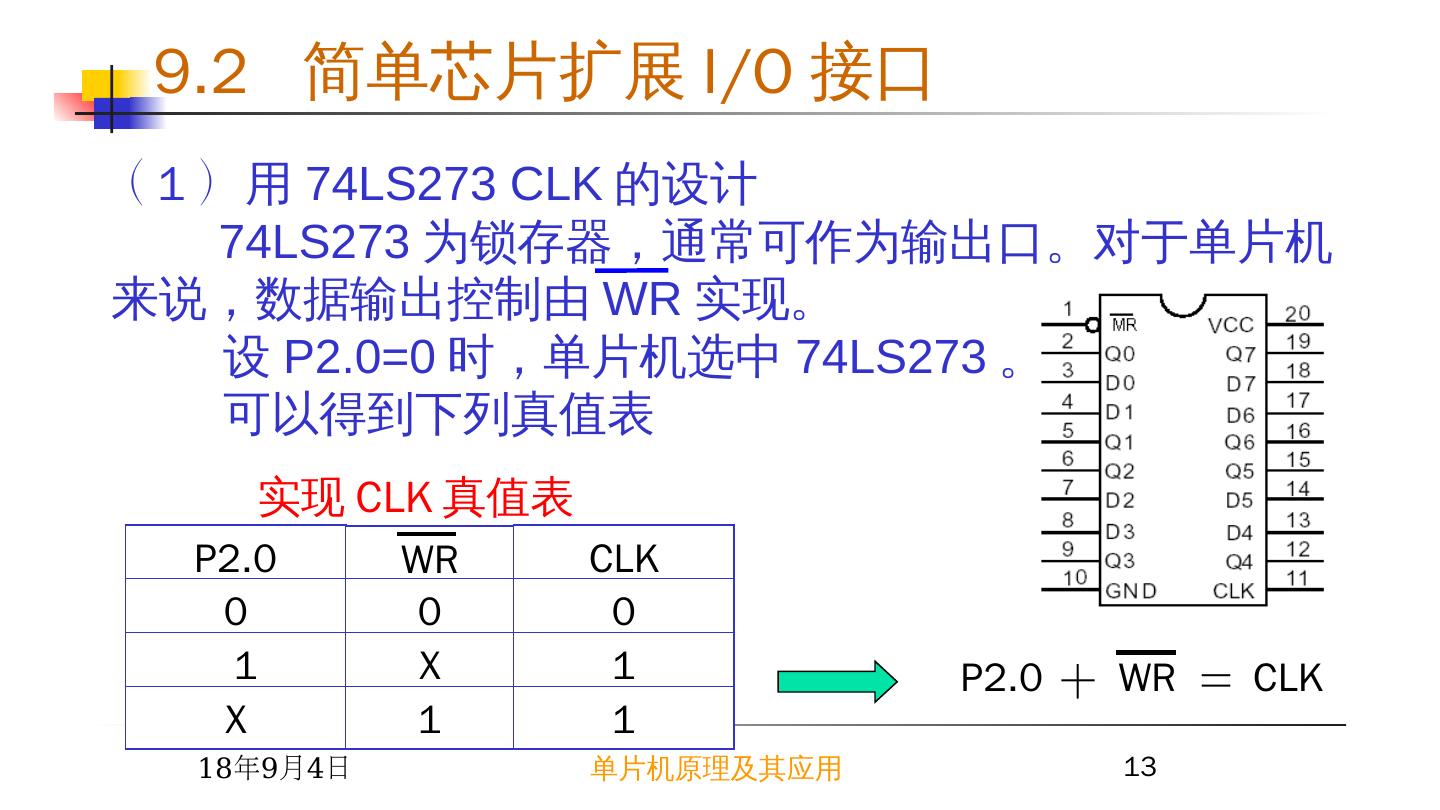

13 .2015/6/23 单片机原理及其应用 13 ( 1 ) 用 74LS273 CLK 的设计 74LS273 为锁存器,通常可作为输出口。对于单片机来说,数据输出控制由 WR 实现。 设 P2.0=0 时,单片机选中 74LS273 。 可以 得到下列真值表 实现 CLK 真值表 P2.0 0 1 WR CLK 0 0 X 1 X 1 1 WR P2.0 + = CLK 9.2 简单芯片扩展 I/O 接口

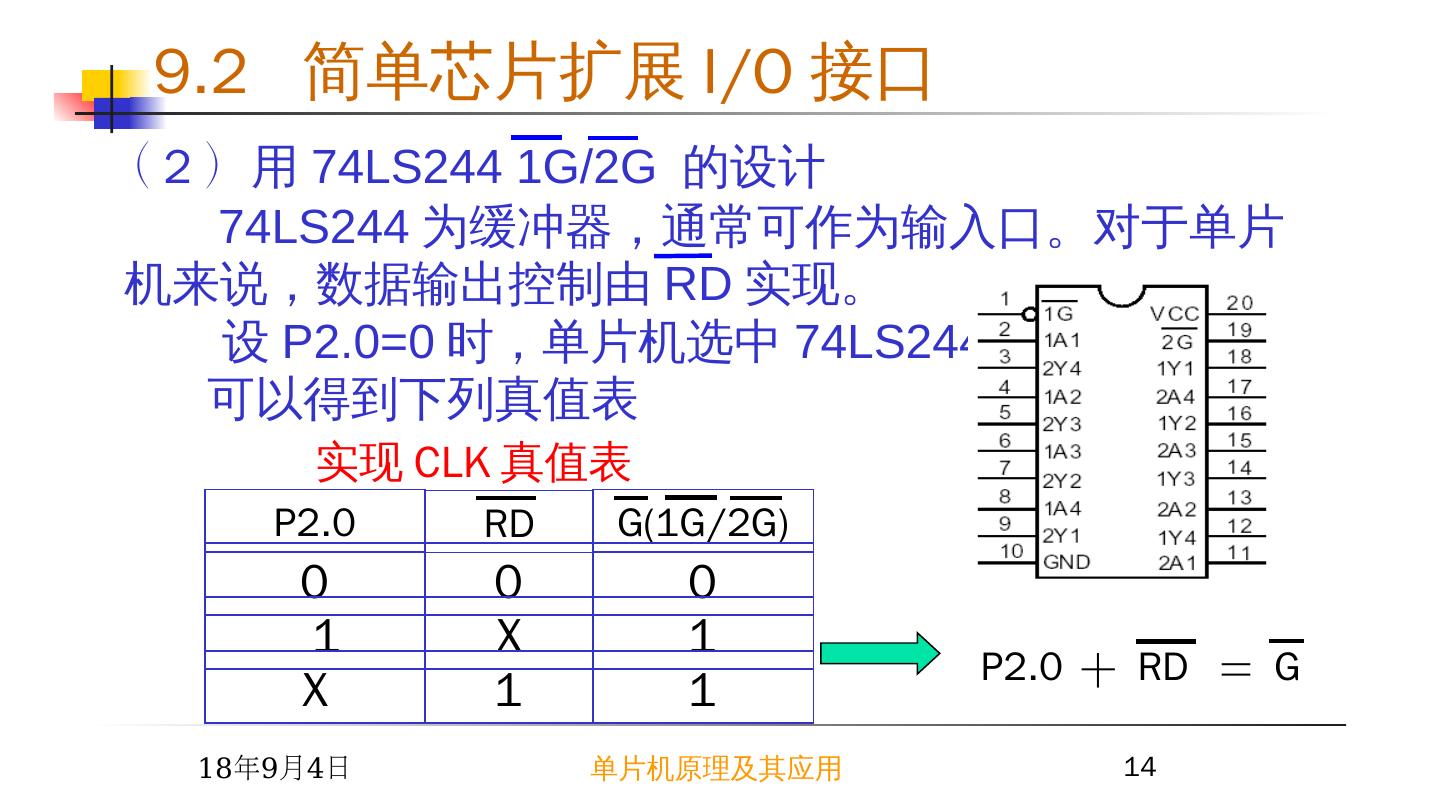

14 .2015/6/23 单片机原理及其应用 14 74LS244 为缓冲器,通常可作为输入口。对于单片机来说,数据输出控制由 RD 实现。 设 P2.0=0 时,单片机选中 74LS244 。 可以 得到下列真值表 实现 CLK 真值表 P2.0 0 1 RD G(1G/2G) 0 0 X 1 X 1 1 RD P2.0 + = G ( 2 ) 用 74LS244 1G/2G 的设计 9.2 简单芯片扩展 I/O 接口

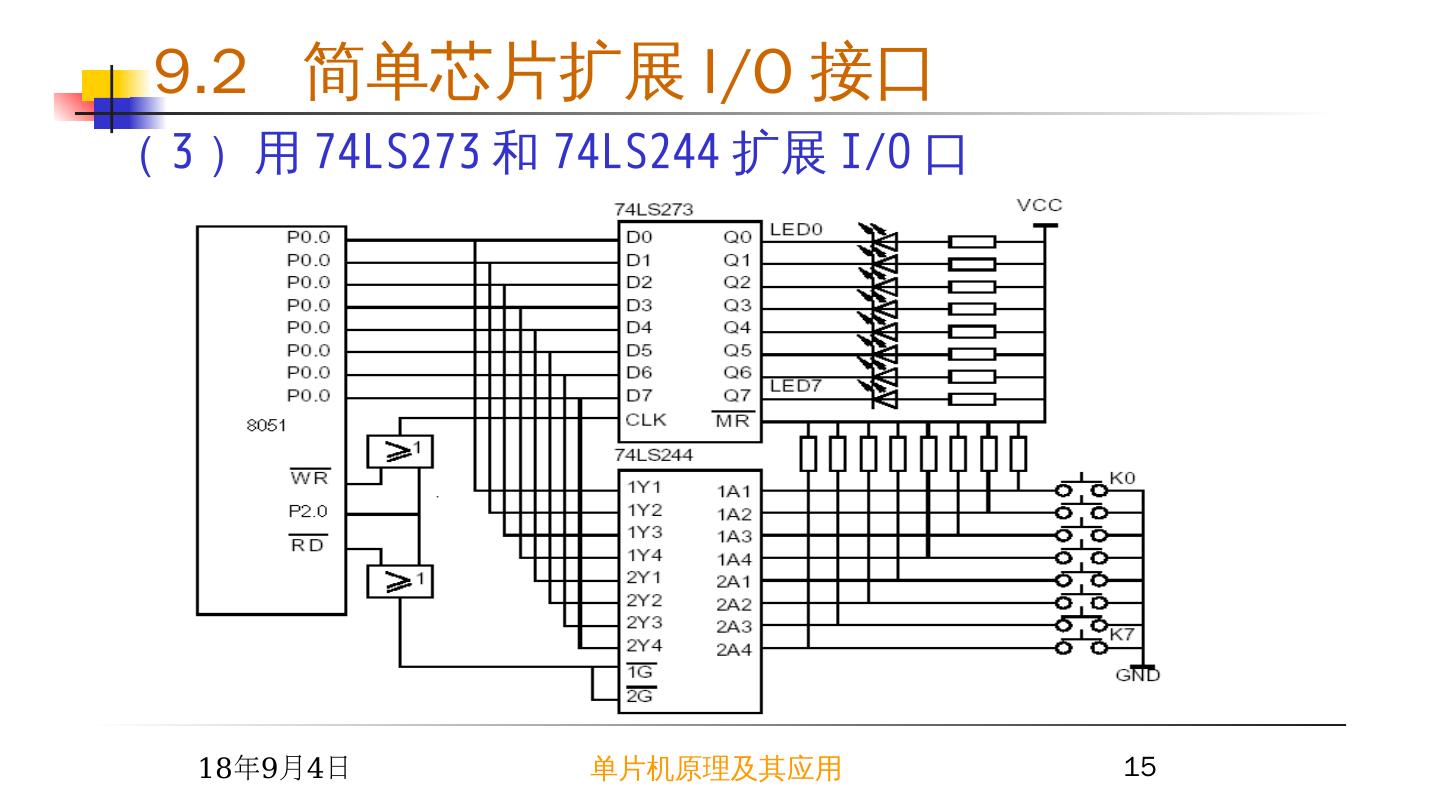

15 .2015/6/23 单片机原理及其应用 15 ( 3 )用 74LS273 和 74LS244 扩展 I/O 口 9.2 简单芯片扩展 I/O 接口

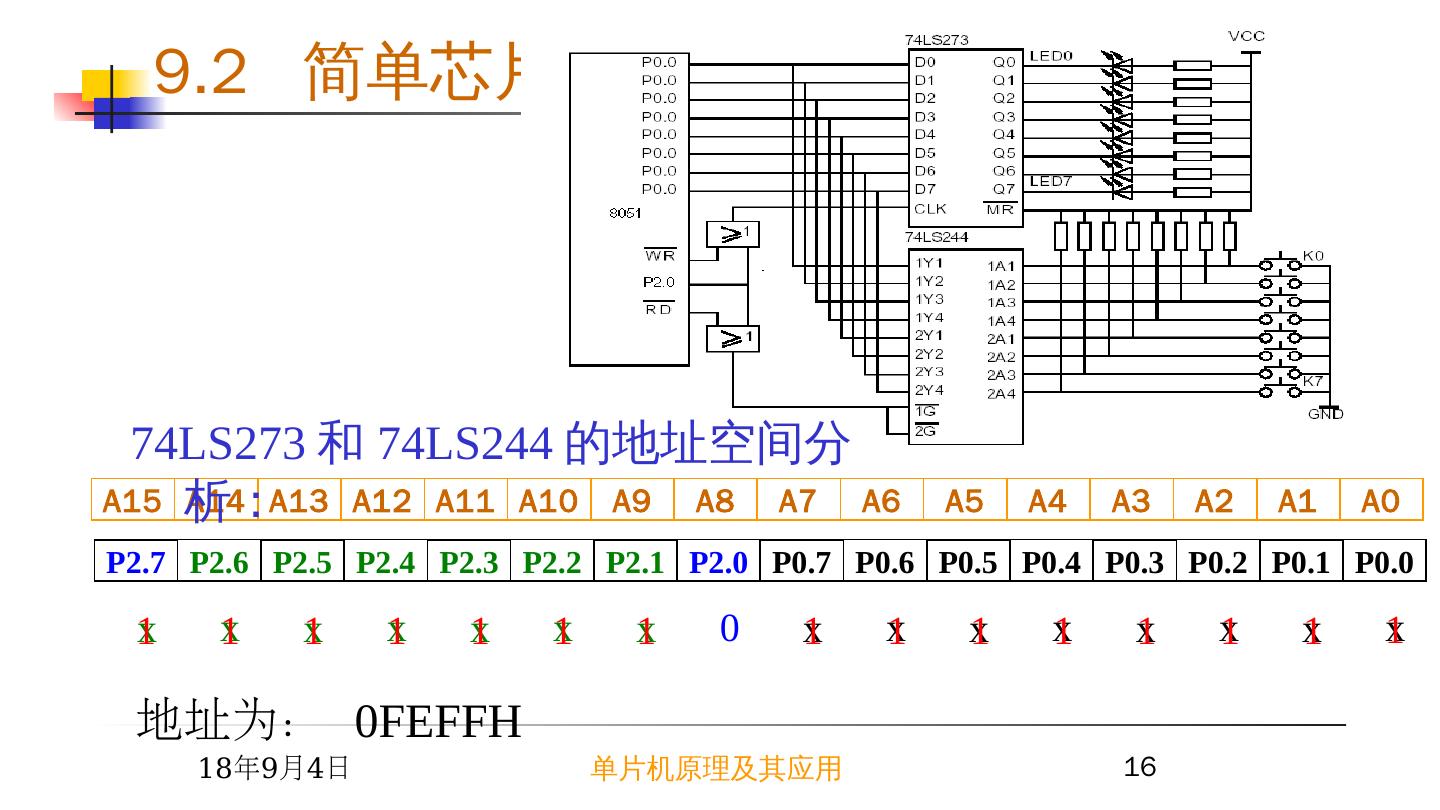

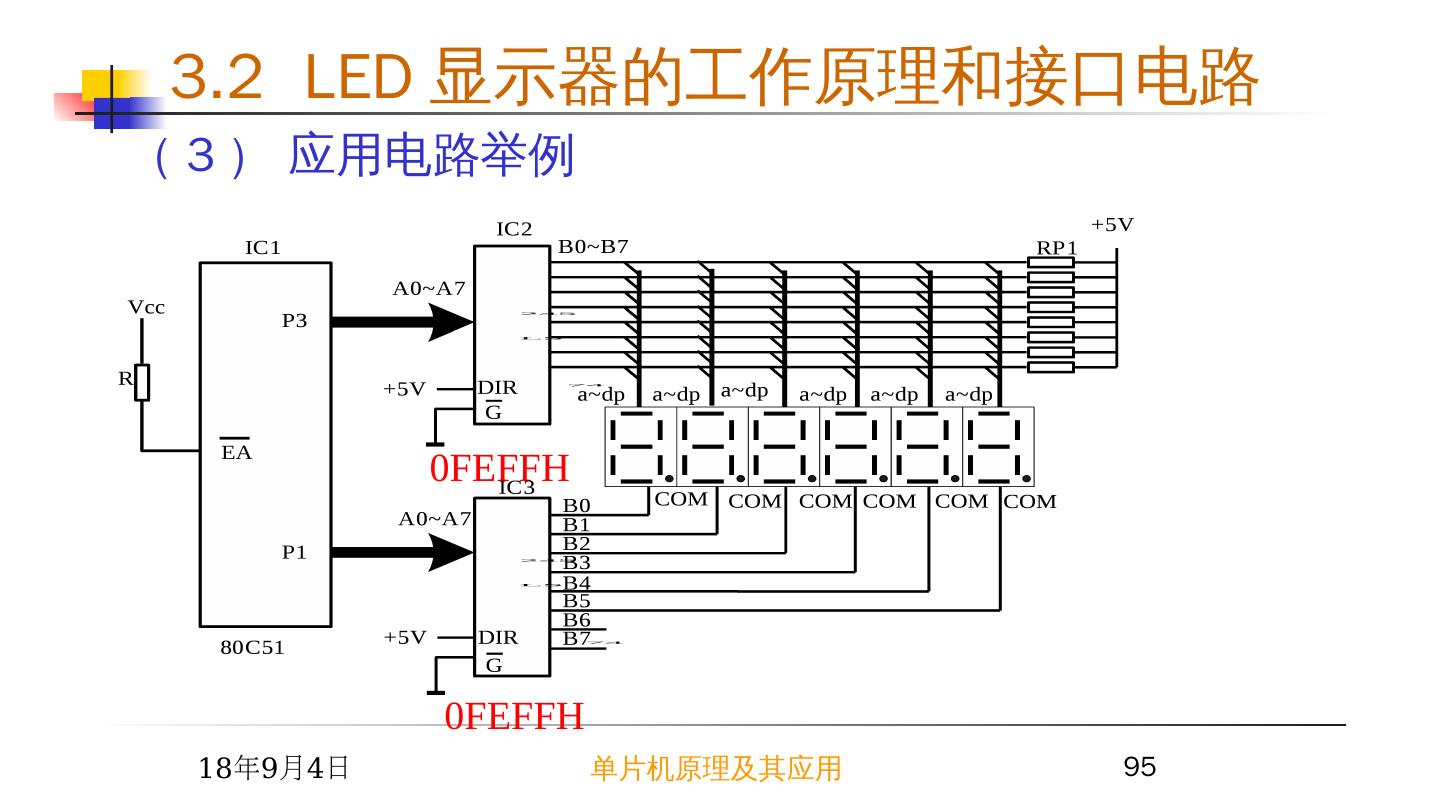

16 .9.2 简单芯片扩展 I/O 接口 2015/6/23 单片机原理及其应用 16 A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0 P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0 x x x x x x x 0 x x x x x x x x 74LS273 和 74LS244 的地址空间分析: 地址为: 0FEFFH 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

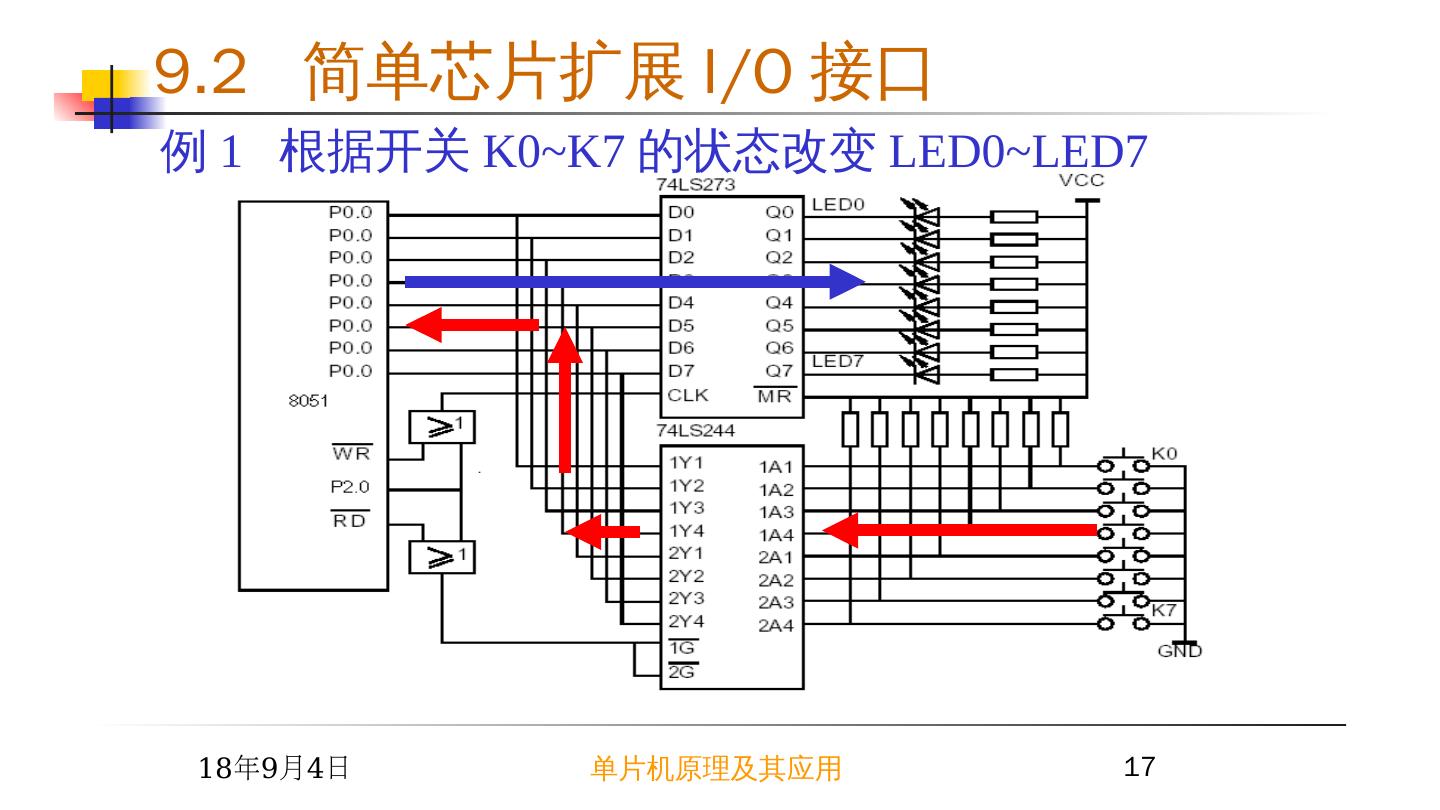

17 .2015/6/23 单片机原理及其应用 17 9.2 简单芯片扩展 I/O 接口 例 1 根据开关 K0~K7 的状态改变 LED0~LED7

18 .9.2 简单芯片扩展 I/O 接口 程序 : MOV DPTR,#0FEFFH MOVX A,@DPTR NOP MOV DPTR,#0FEFFH MOVX @DPTR,A RET 2015/6/23 单片机原理及其应用 18 例 1 根据开关 K0~K7 的状态改变 LED0~LED7

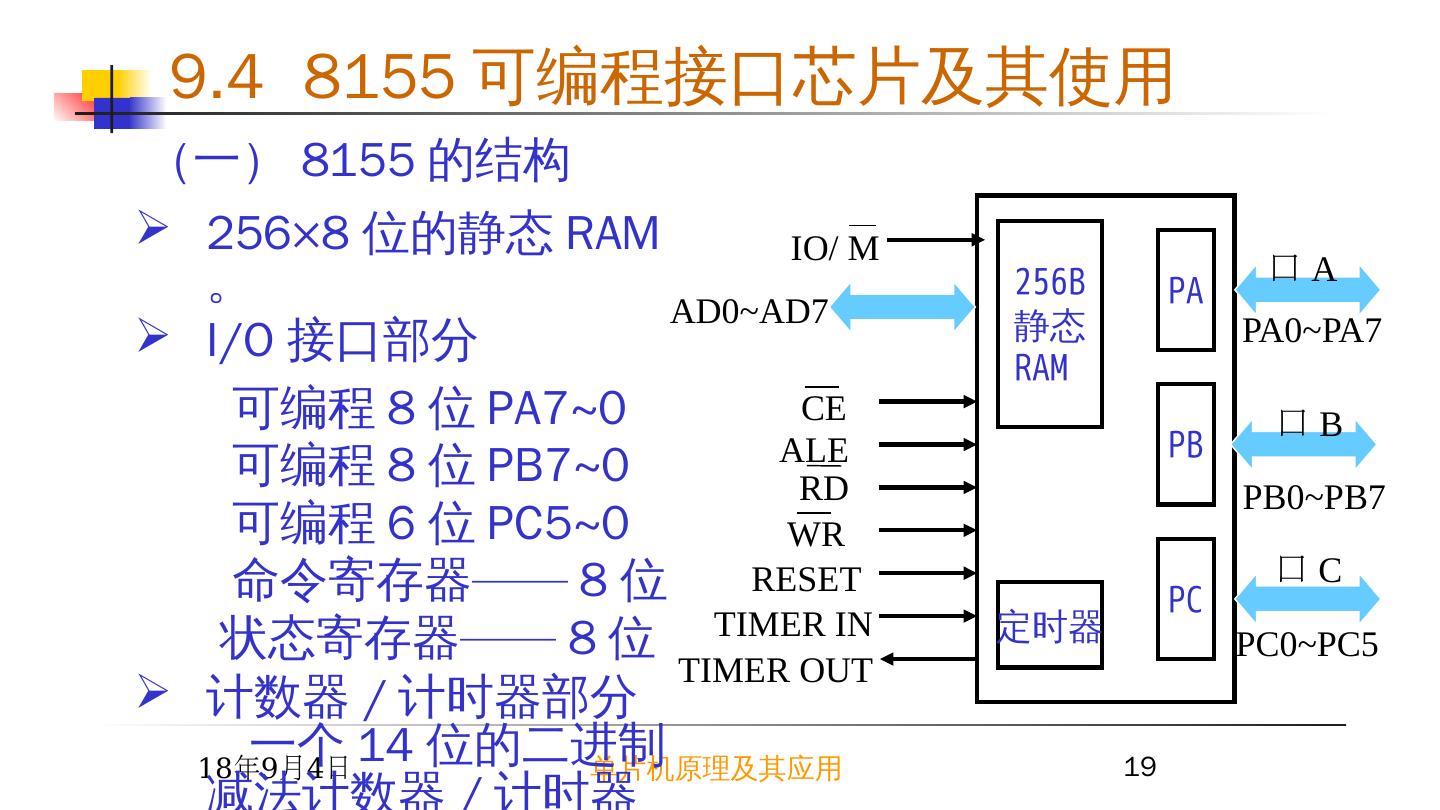

19 .2015/6/23 单片机原理及其应用 19 256 × 8 位的静态 RAM 。 I/O 接口部分 可编程 8 位 PA7~0 可编程 8 位 PB7~0 可编程 6 位 PC5~0 命令寄存器 —— 8 位 状态寄存器 —— 8 位 计数器 / 计时器部分 一个 14 位的二进制减法计数器 / 计时器 256B 静态 RAM PA 定时器 PB PC 口 A PA0~PA7 口 B PB0~PB7 PC0~PC5 口 C IO/ M AD0~AD7 TIMER IN TIMER OUT CE ALE RD WR RESET (一) 8155 的结构 9.4 8155 可编程接口芯片及其使用

20 .2015/6/23 单片机原理及其应用 20 TIMER IN TIMER OUT PC3 PC4 PC5 IO/ M CE RD WR ALE AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 Vss Vcc PC2 PC1 PC0 PB7 PB6 PB5 PB4 PB3 PB2 PB1 PB0 PA7 PA6 PA5 PA4 PA3 PA2 PA1 PA0 8155 RESET AD 7~ 0 -地址数据线,三态 RESET - 复位信号 ALE - 允许地址锁存信号 CE - 片选信号 IO/M - 接口与存储器的选择信号 WR - 写信号 RD - 读信号 (二) 8155 的引脚 9.4 8155 可编程接口芯片及其使用

21 .2015/6/23 单片机原理及其应用 21 PA7~0 - 8 根通用的 I/O 端口线 PB7~0 - 8 根通用的 I/O 端口线 PC5~0 - 6 根通用的 I/O 端口线 TIMERIN - 14 位二进制减法 计数器的输入端 TIMEROUT -计时器的输出引脚 TIMER IN TIMER OUT PC3 PC4 PC5 IO/ M CE RD WR ALE AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 Vss Vcc PC2 PC1 PC0 PB7 PB6 PB5 PB4 PB3 PB2 PB1 PB0 PA7 PA6 PA5 PA4 PA3 PA2 PA1 PA0 8155 RESET 电源引脚: Vcc , Vss 9.4 8155 可编程接口芯片及其使用

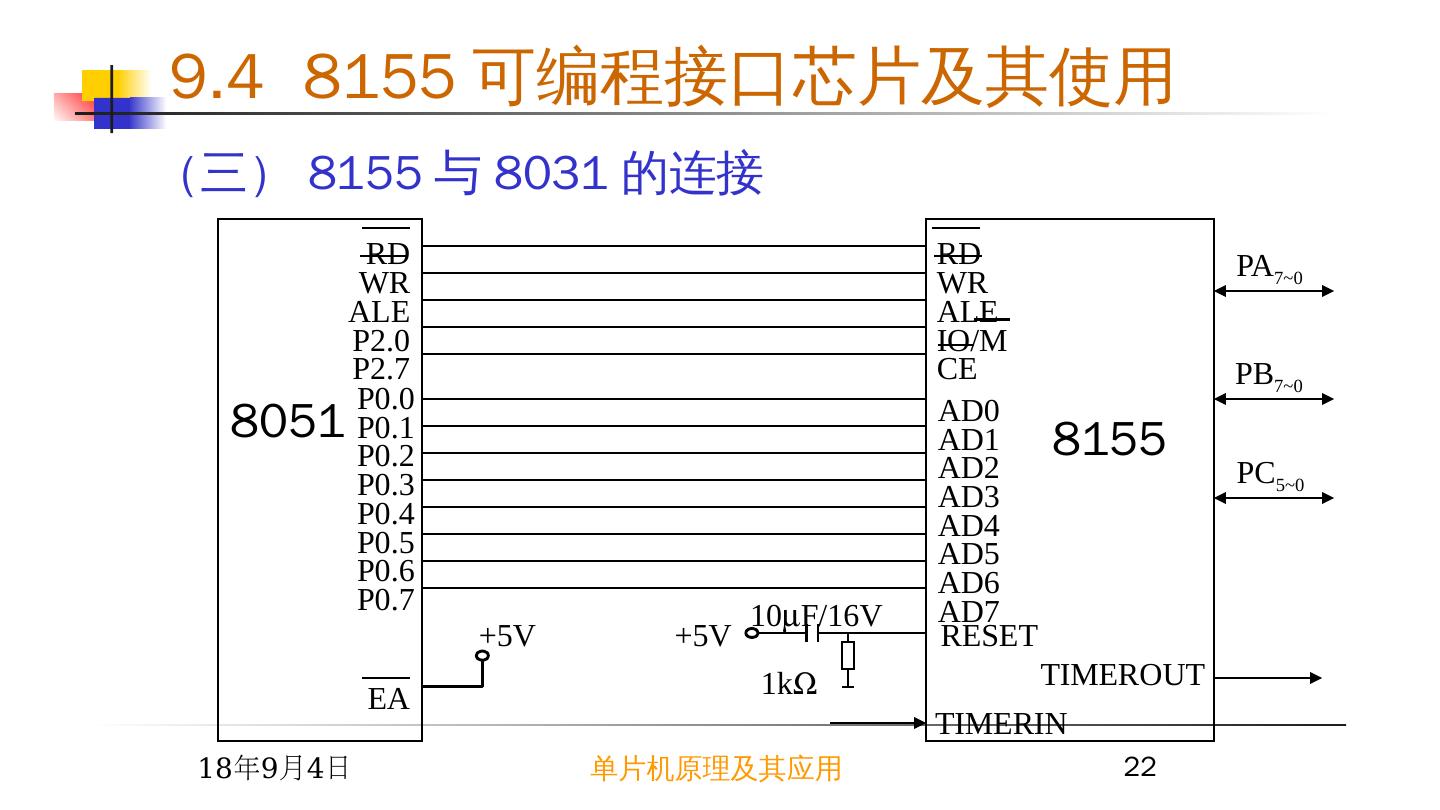

22 .2015/6/23 单片机原理及其应用 22 (三) 8155 与 8031 的连接 9.4 8155 可编程接口芯片及其使用 RD WR ALE P2.0 P2.7 P0.0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7 EA RD WR ALE IO/M CE AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 RESET TIMERIN TIMEROUT +5V 10 F/16V 1k PA 7~0 PB 7~0 PC 5~0 8051 8155 +5V

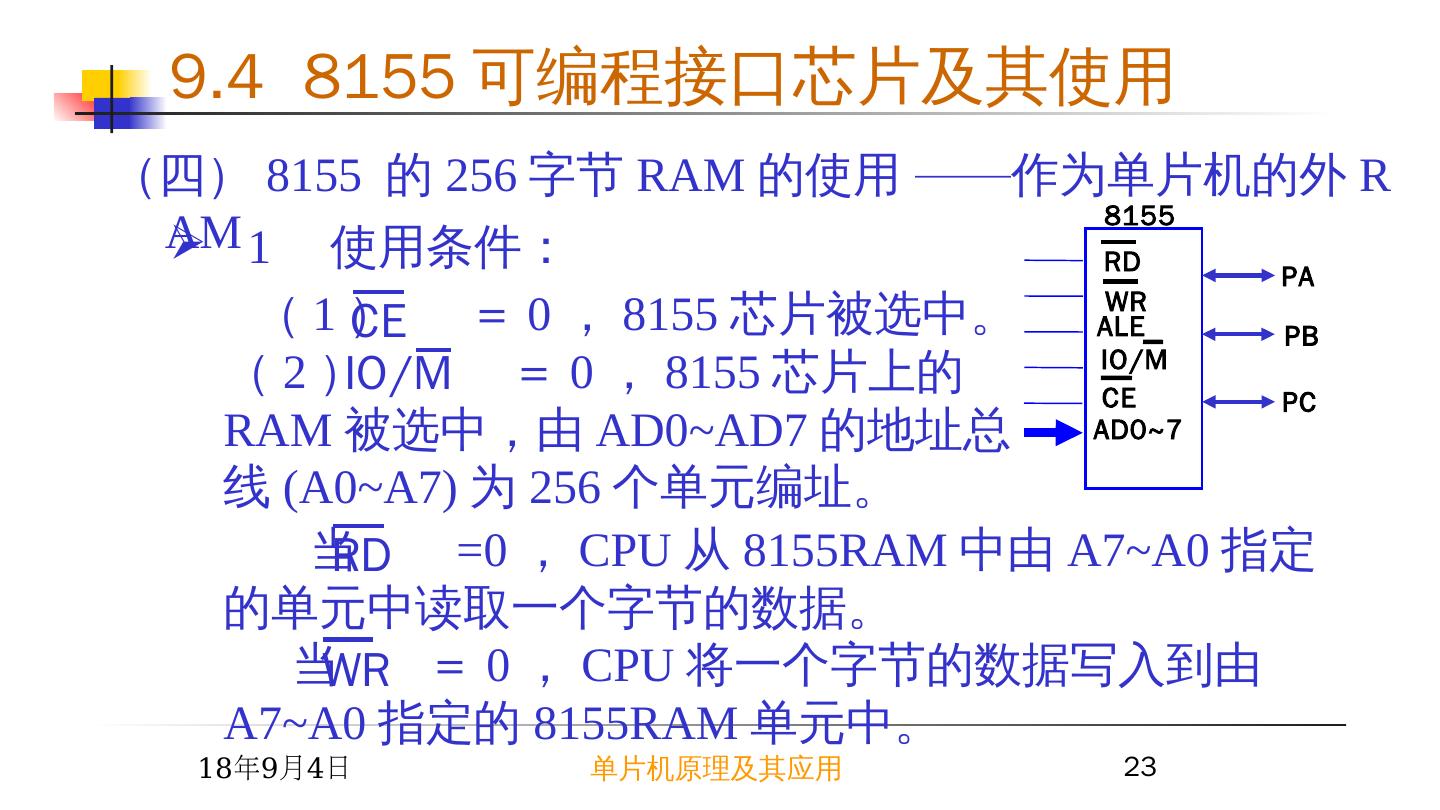

23 . 1 使用条件: ( 1 ) = 0 , 8155 芯片被选中。 ( 2 ) = 0 , 8155 芯片上的 RAM 被选中,由 AD0~AD7 的地址总线 (A0~A7) 为 256 个单元编址。 2015/6/23 单片机原理及其应用 23 (四) 8155 的 256 字节 RAM 的使用 —— 作为单片机的外 RAM 8155 RD WR CE IO/M ALE AD0~7 PA PB PC CE IO/M 当 =0 , CPU 从 8155RAM 中由 A7~A0 指定的单元中读取一个字节的数据。 当 = 0 , CPU 将一个字节的数据写入到由 A7~A0 指定的 8155RAM 单元中。 RD WR 9.4 8155 可编程接口芯片及其使用

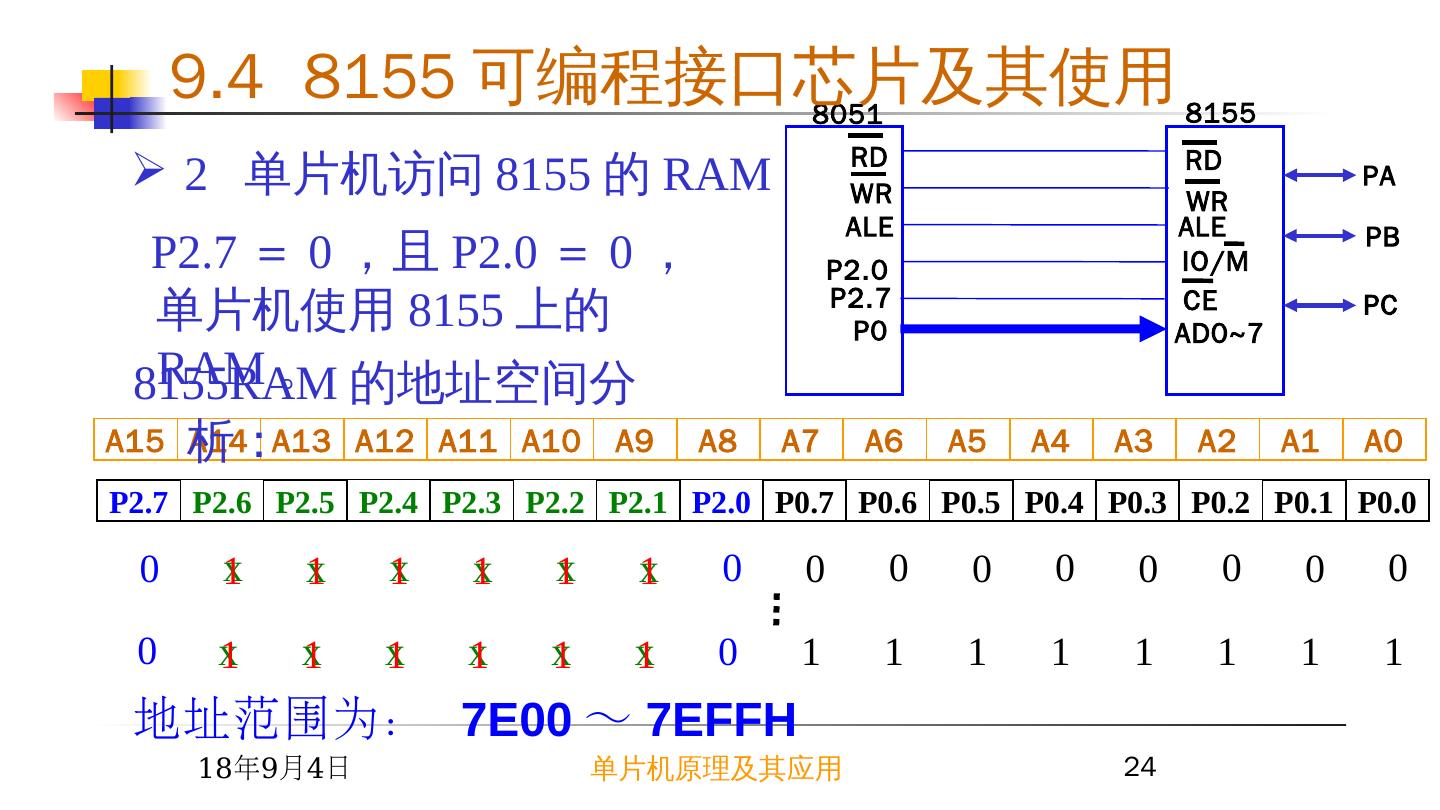

24 .2015/6/23 单片机原理及其应用 24 2 单片机访问 8155 的 RAM 8051 RD WR ALE P2.0 P2.7 P0 8155 RD WR CE IO/M ALE AD0~7 PA PB PC P2.7 = 0 ,且 P2.0 = 0 ,单片机使用 8155 上的 RAM 。 A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0 P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0 0 x x x x x x 0 0 0 0 0 0 0 0 0 x x x x x x 0 1 1 1 1 1 1 1 1 0 8155RAM 的地址空间分析: 地址范围为: 7E00 ~ 7EFFH 1 1 1 1 1 1 1 1 1 1 1 1 9.4 8155 可编程接口芯片及其使用

25 .2015/6/23 单片机原理及其应用 25 3 单片机访问 8155RAM 的程序设计 8051 RD WR ALE P2.0 P2.7 P0 8155 RD WR CE IO/M ALE AD0~7 PA PB PC 9.4 8155 可编程接口芯片及其使用 RAM 地址 范围为: 7E00 ~ 7EFFH

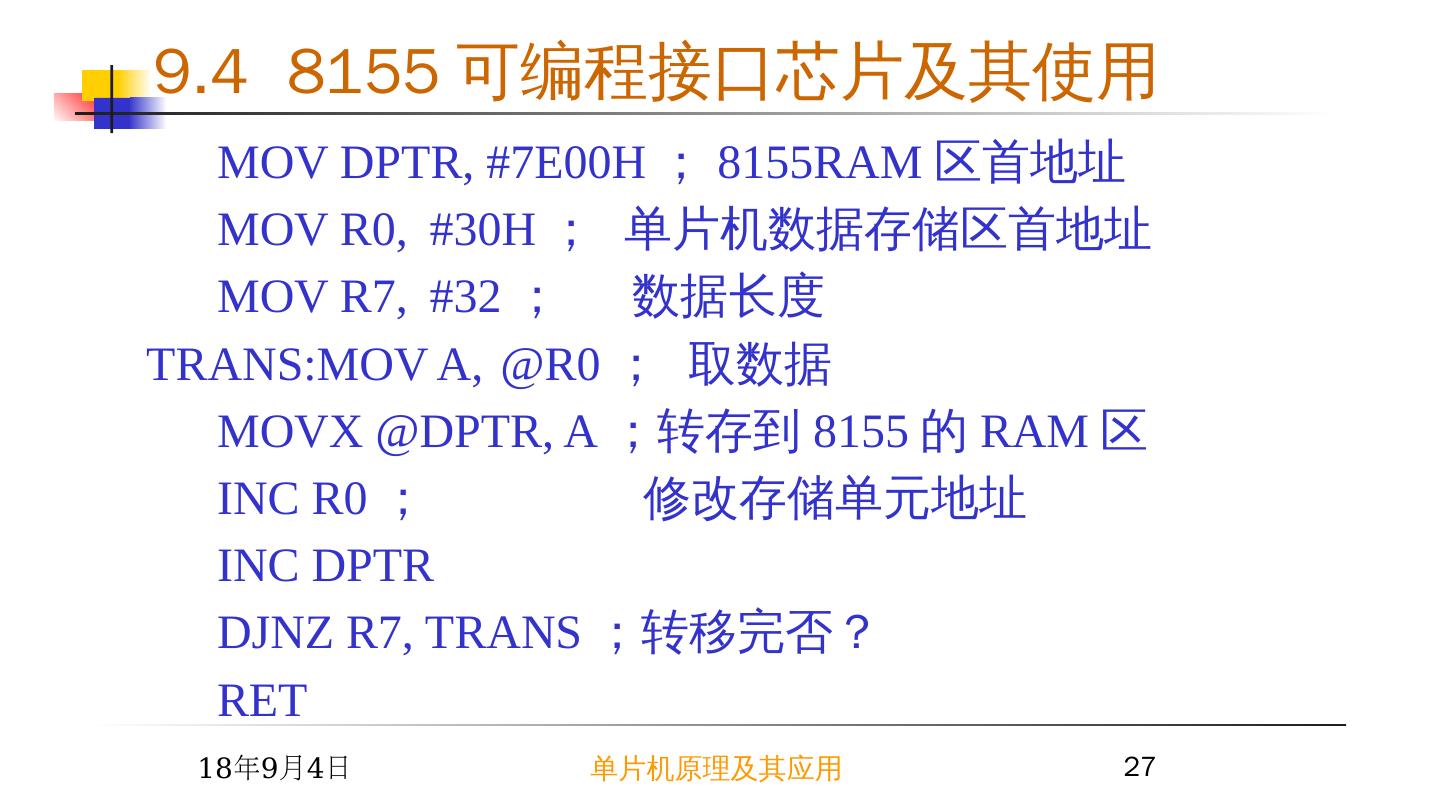

26 .9.4 8155 可编程接口芯片 及其 例 2 把 单片机内部 RAM 中从 30H 单元开始存储的 32 个字节数据转移到 8155 芯片上的 RAM 区中 程序 2015/6/23 单片机原理及其应用 26 8051 RD WR ALE P2.0 P2.7 P0 8155 RD WR CE IO/M ALE AD0~7 PA PB PC RAM 地址 范围为: 7E00 ~ 7E1EH

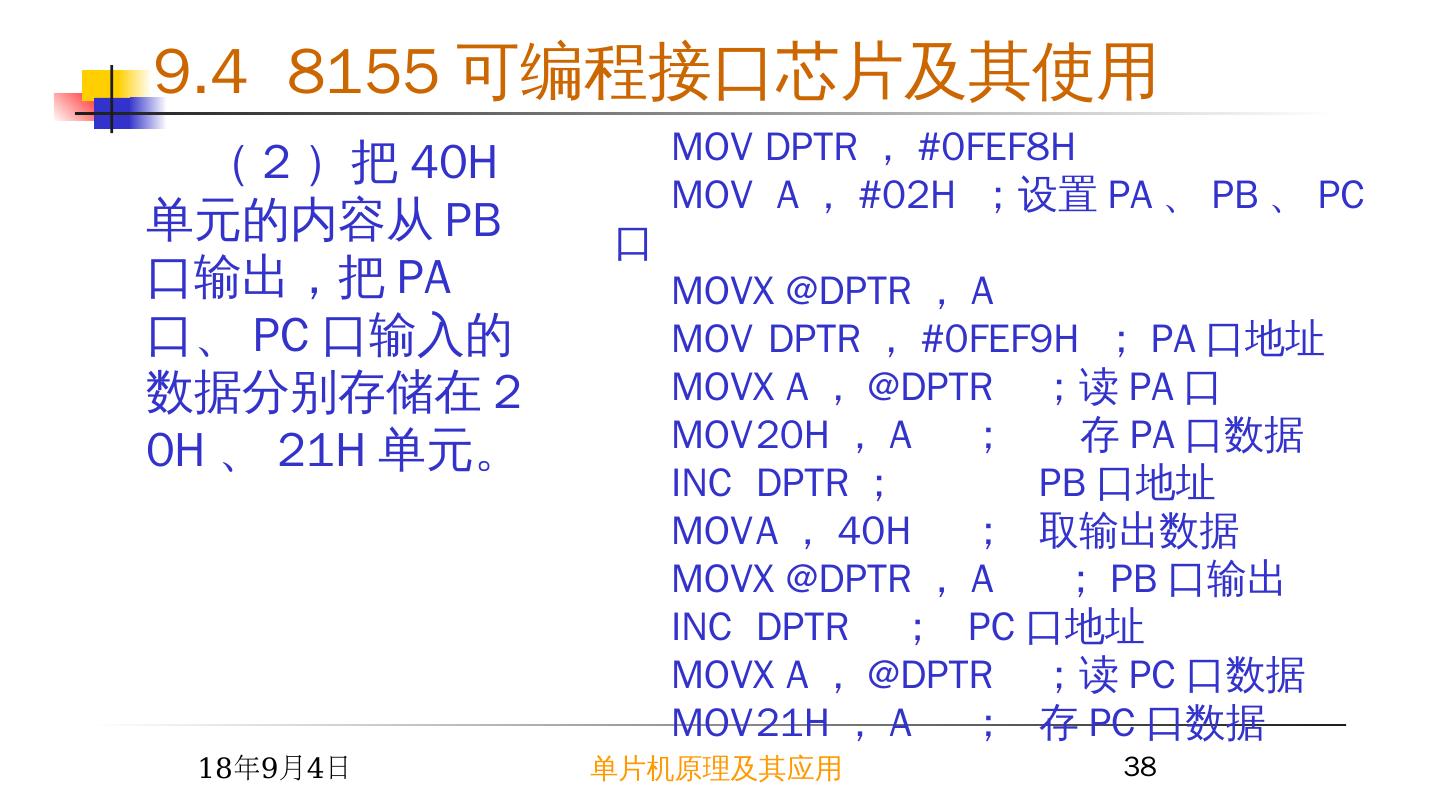

27 .9.4 8155 可编程接口芯片 及其使用 MOV DPTR, #7E00H ; 8155RAM 区首地址 MOV R0, #30H ; 单片机 数据存储区首地址 MOV R7, #32 ; 数据 长度 TRANS:MOV A, @R0 ; 取 数据 MOVX @DPTR, A ;转存到 8155 的 RAM 区 INC R0 ; 修改 存储单元地址 INC DPTR DJNZ R7, TRANS ;转移完否? RET 2015/6/23 单片机原理及其应用 27

28 .1 使用条件 : ( 1 ) = 0 , 8155 芯片被选中。 ( 2 ) = 1 , 8155 芯片上的 I/O 口和定时 / 计数器被选中,由 AD0~AD7 的地址总线 (A0~A2) 为 I/O 口和定时 / 计数器编址。 2015/6/23 单片机原理及其应用 28 (五) 8155 的 I/O 端口使用 —— 作为单片机的外部 I/O 口 8155 RD WR CE IO/M ALE AD0~7 PA PB PC CE IO/M 当 =0 , CPU 从 A2~A0 指定的对象读取(输入)一个字节的数据。 当 = 0 , CPU 将一个字节的数据写入(输出)到 A2~A0 指定的对象。 RD WR 9.4 8155 可编程接口芯片及其使用

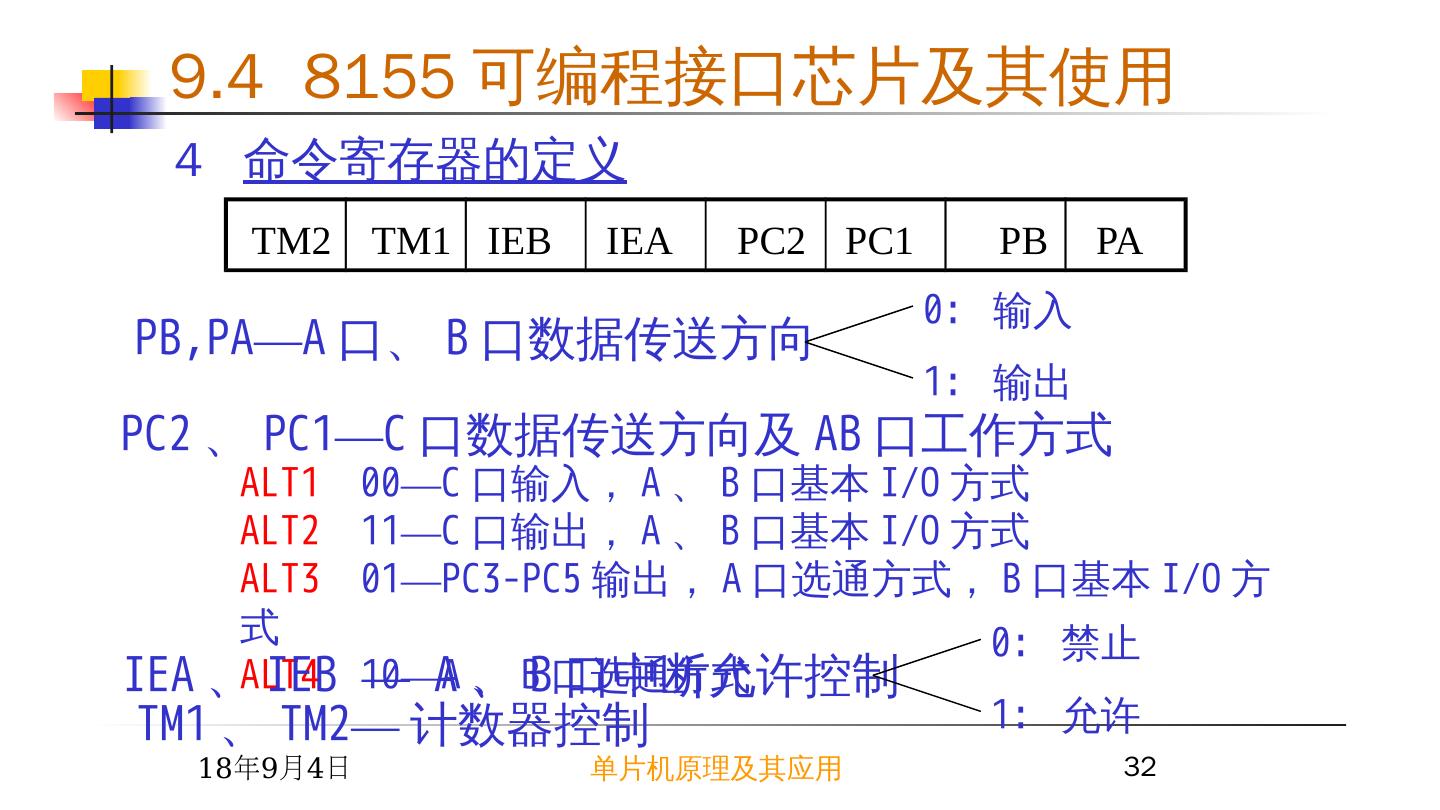

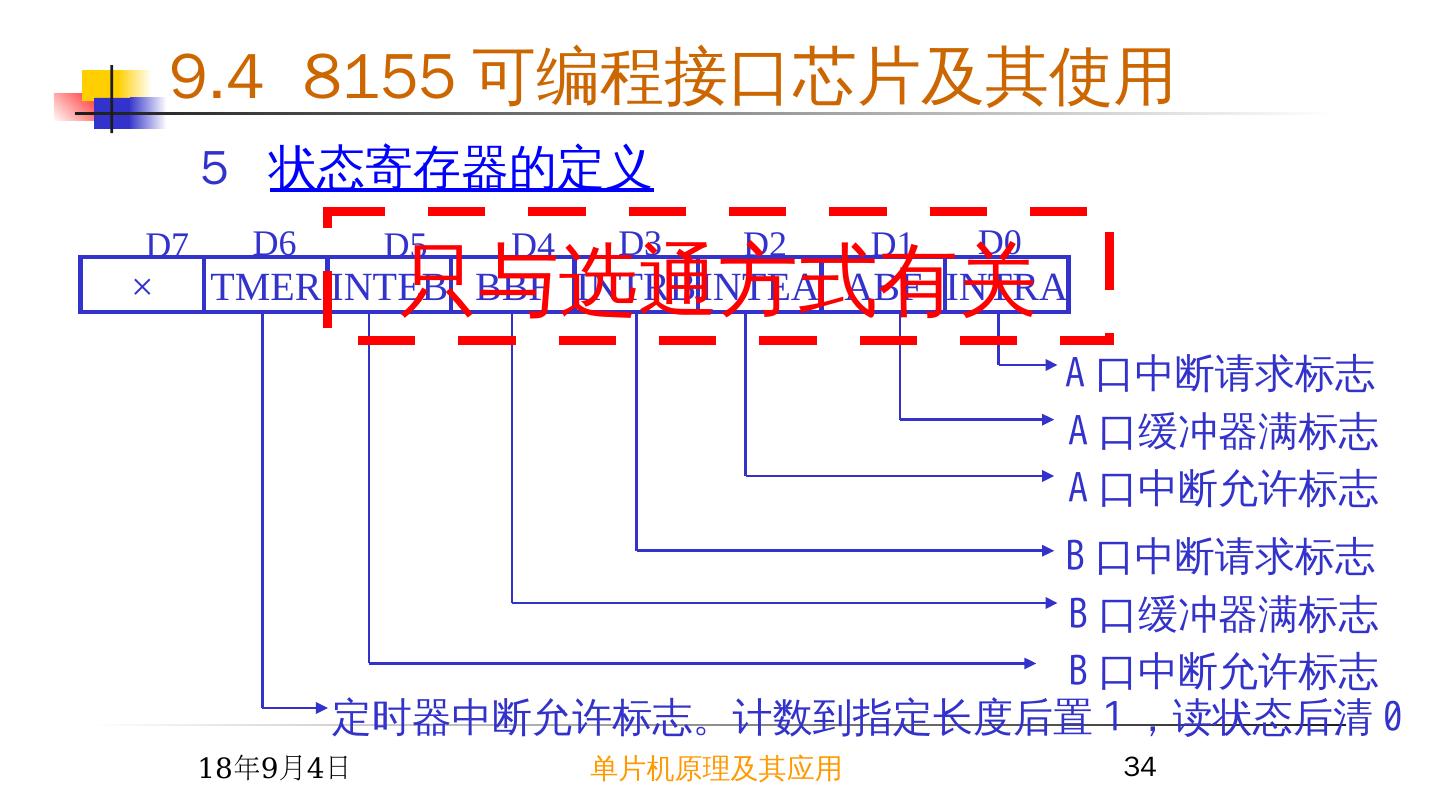

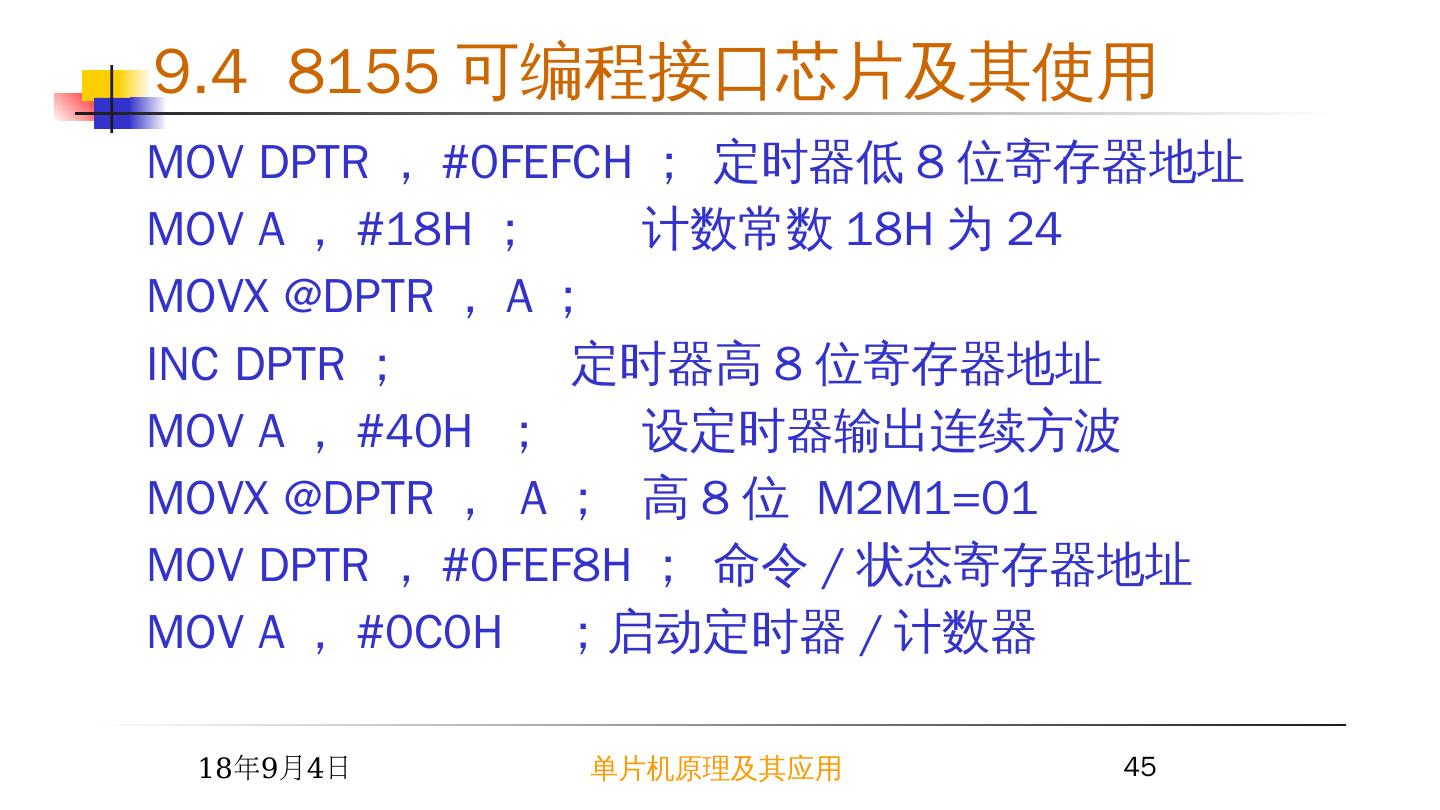

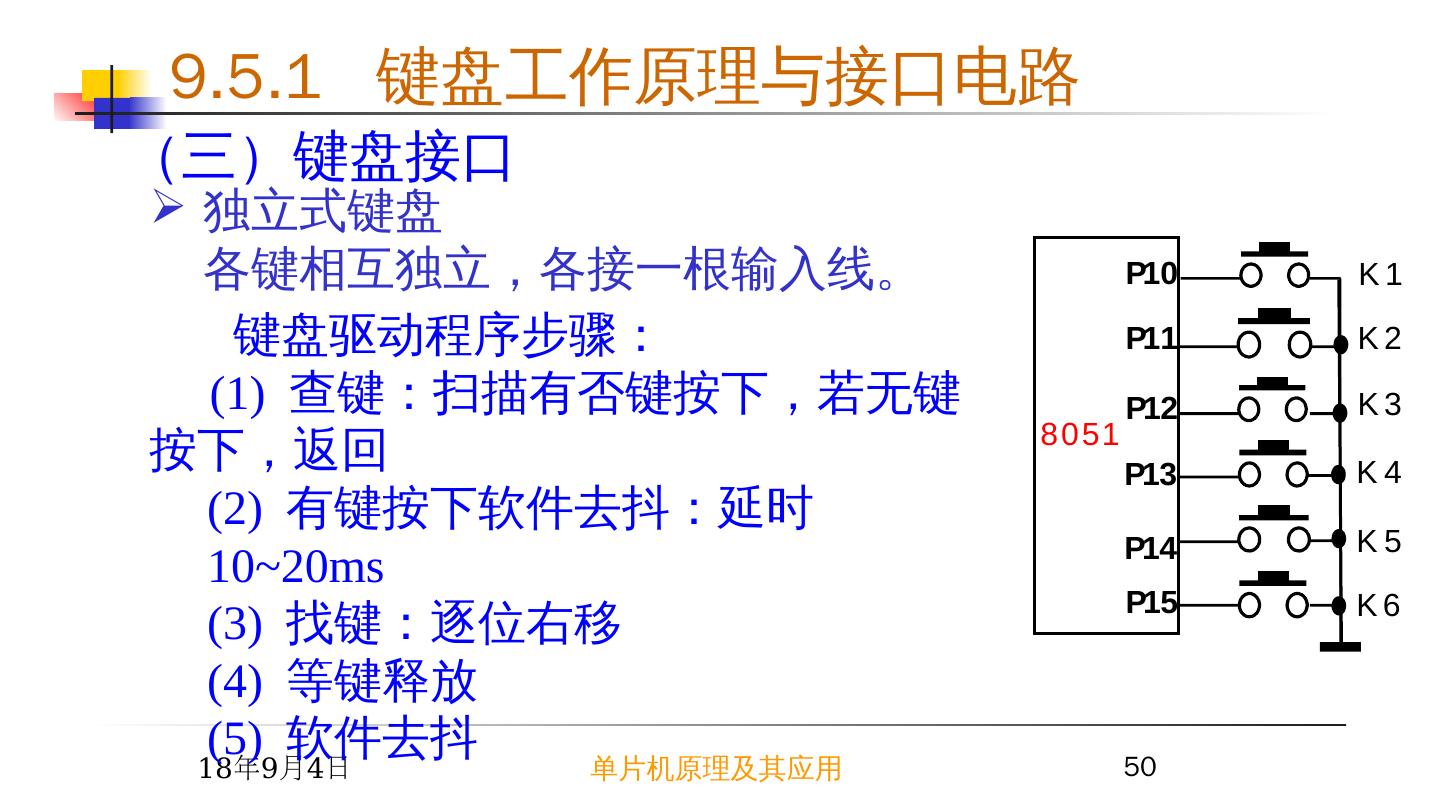

29 .2015/6/23 单片机原理及其应用 29 2 8155 芯片 I/O 口地址分配 A7 A6 A5 A4 A3 A2 A1 A0 I/O 端口 ╳ ╳ ╳ ╳ ╳ 0 0 0 命令 / 状态寄存器 ╳ ╳ ╳ ╳ ╳ 0 0 1 A 口 ╳ ╳ ╳ ╳ ╳ 0 1 0 B 口 ╳ ╳ ╳ ╳ ╳ 0 1 1 C 口 ╳ ╳ ╳ ╳ ╳ 1 0 0 计数器低 8 位 ╳ ╳ ╳ ╳ ╳ 1 0 1 计数器高 6 位 9.4 8155 可编程接口芯片及其使用