- 快召唤伙伴们来围观吧

- 微博 QQ QQ空间 贴吧

- 文档嵌入链接

- <iframe src="https://www.slidestalk.com/u214/LC3_Data_Movement_Instructions?embed" frame border="0" width="640" height="360" scrolling="no" allowfullscreen="true">复制

- 微信扫一扫分享

LC3数据移动指令

展开查看详情

1 .Chapter 5 The LC-3

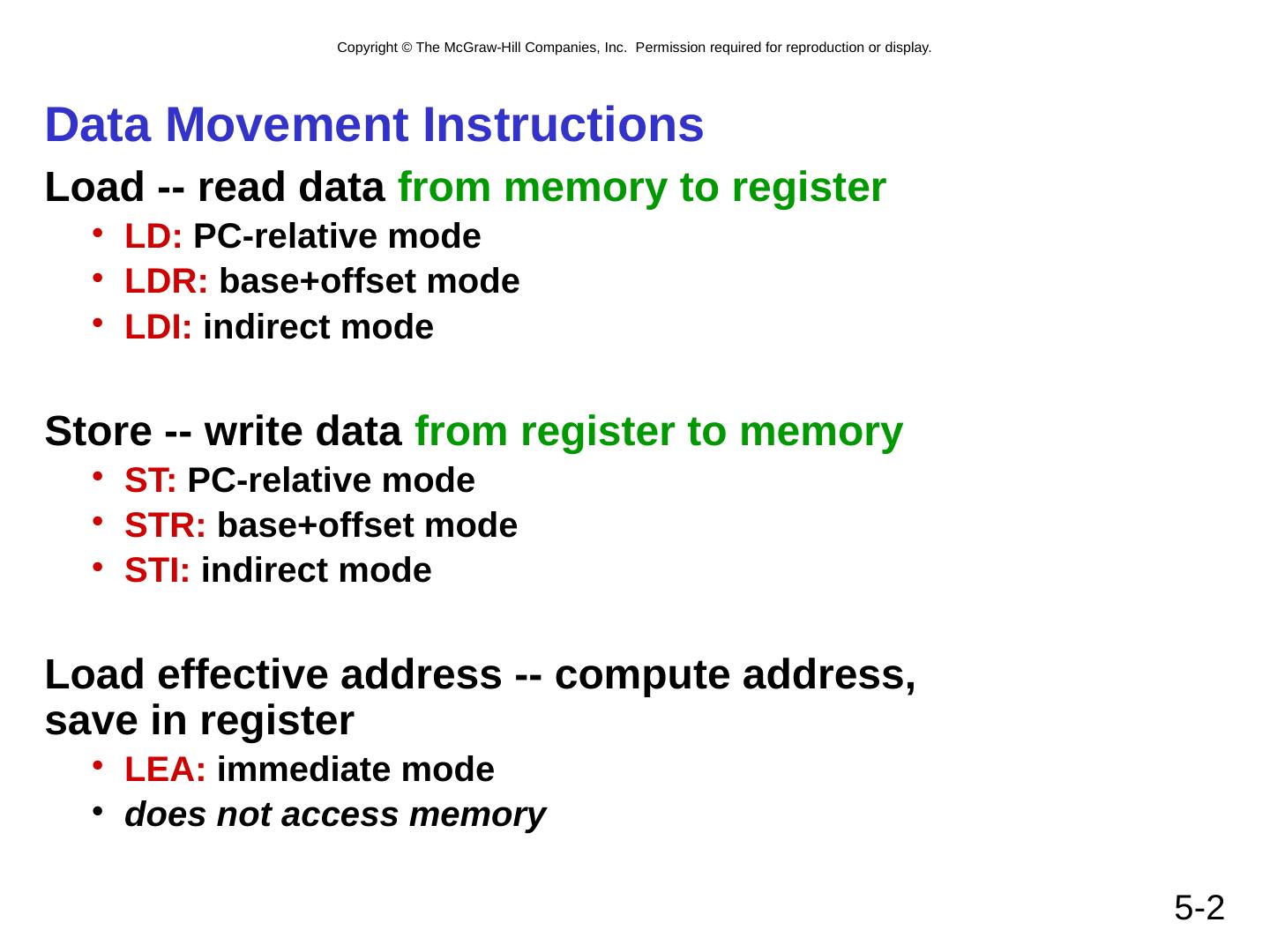

2 .5- 2 Data Movement Instructions Load -- read data from memory to register LD: PC-relative mode LDR: base+offset mode LDI: indirect mode Store -- write data from register to memory ST: PC-relative mode STR: base+offset mode STI: indirect mode Load effective address -- compute address, save in register LEA: immediate mode does not access memory

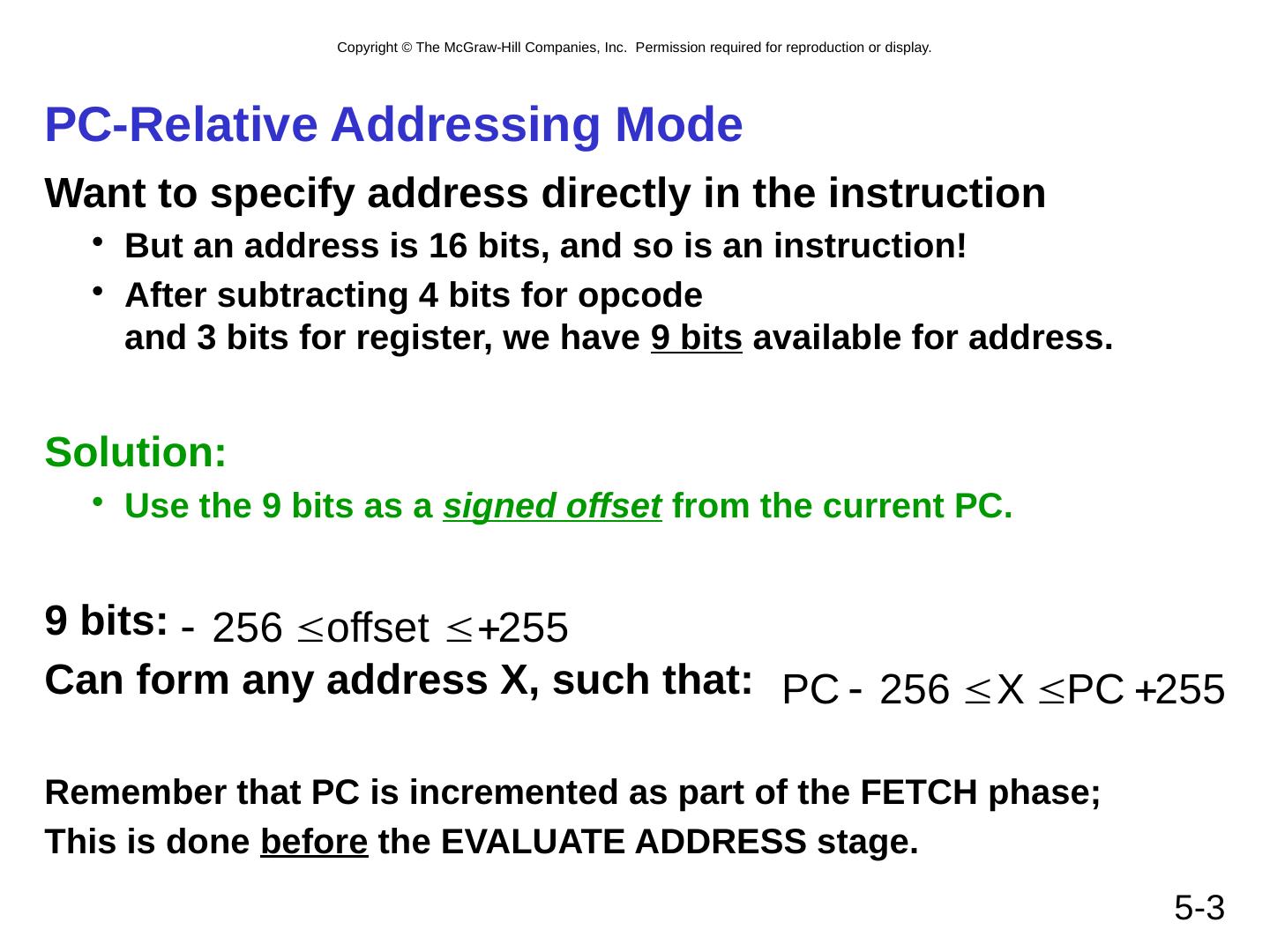

3 .5- 3 PC-Relative Addressing Mode Want to specify address directly in the instruction But an address is 16 bits, and so is an instruction! After subtracting 4 bits for opcode and 3 bits for register, we have 9 bits available for address. Solution: Use the 9 bits as a signed offset from the current PC. 9 bits: Can form any address X, such that: Remember that PC is incremented as part of the FETCH phase; This is done before the EVALUATE ADDRESS stage.

4 .5- 4 LD (PC-Relative ) R Dst <- M [ PC + IR[8:0] ] Note: The ALU is shown performing the add, but there may be a separate adder for address generation.

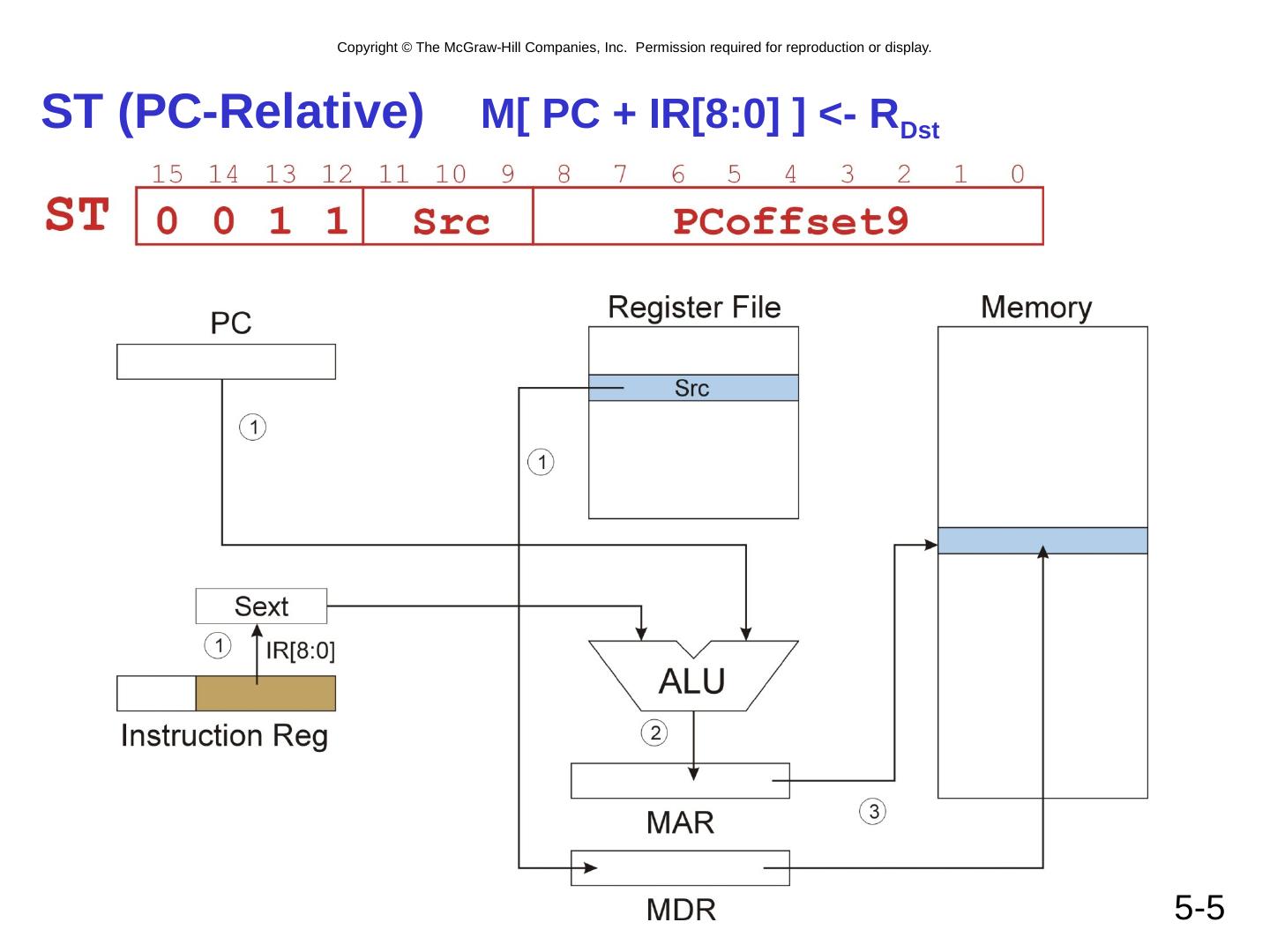

5 .5- 5 ST (PC-Relative ) M [ PC + IR[8:0 ] ] <- R Dst

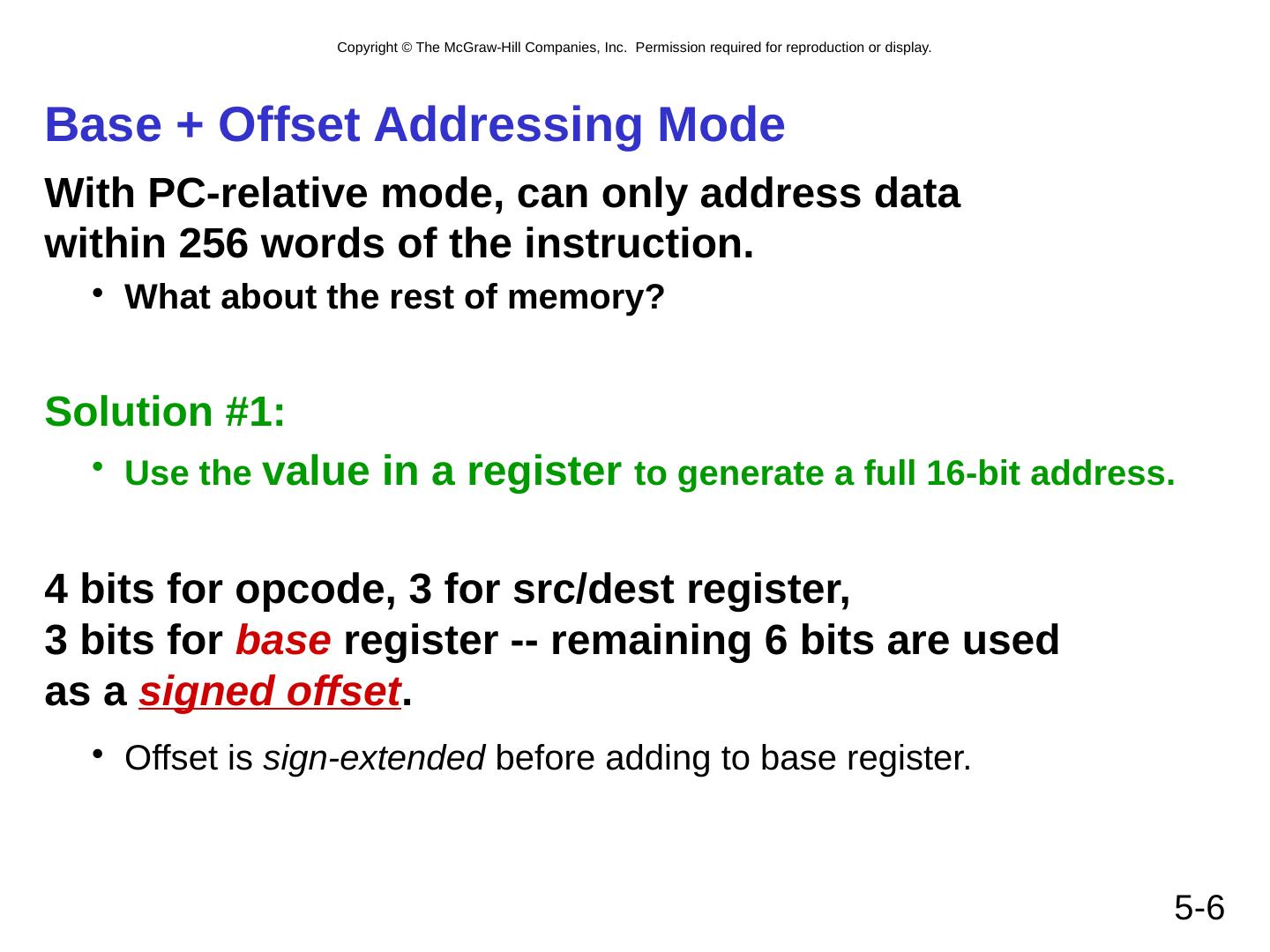

6 .5- 6 Base + Offset Addressing Mode With PC-relative mode, can only address data within 256 words of the instruction. What about the rest of memory? Solution #1: Use the value in a register to generate a full 16-bit address. 4 bits for opcode , 3 for src / dest register, 3 bits for base register -- remaining 6 bits are used as a signed offset . Offset is sign-extended before adding to base register.

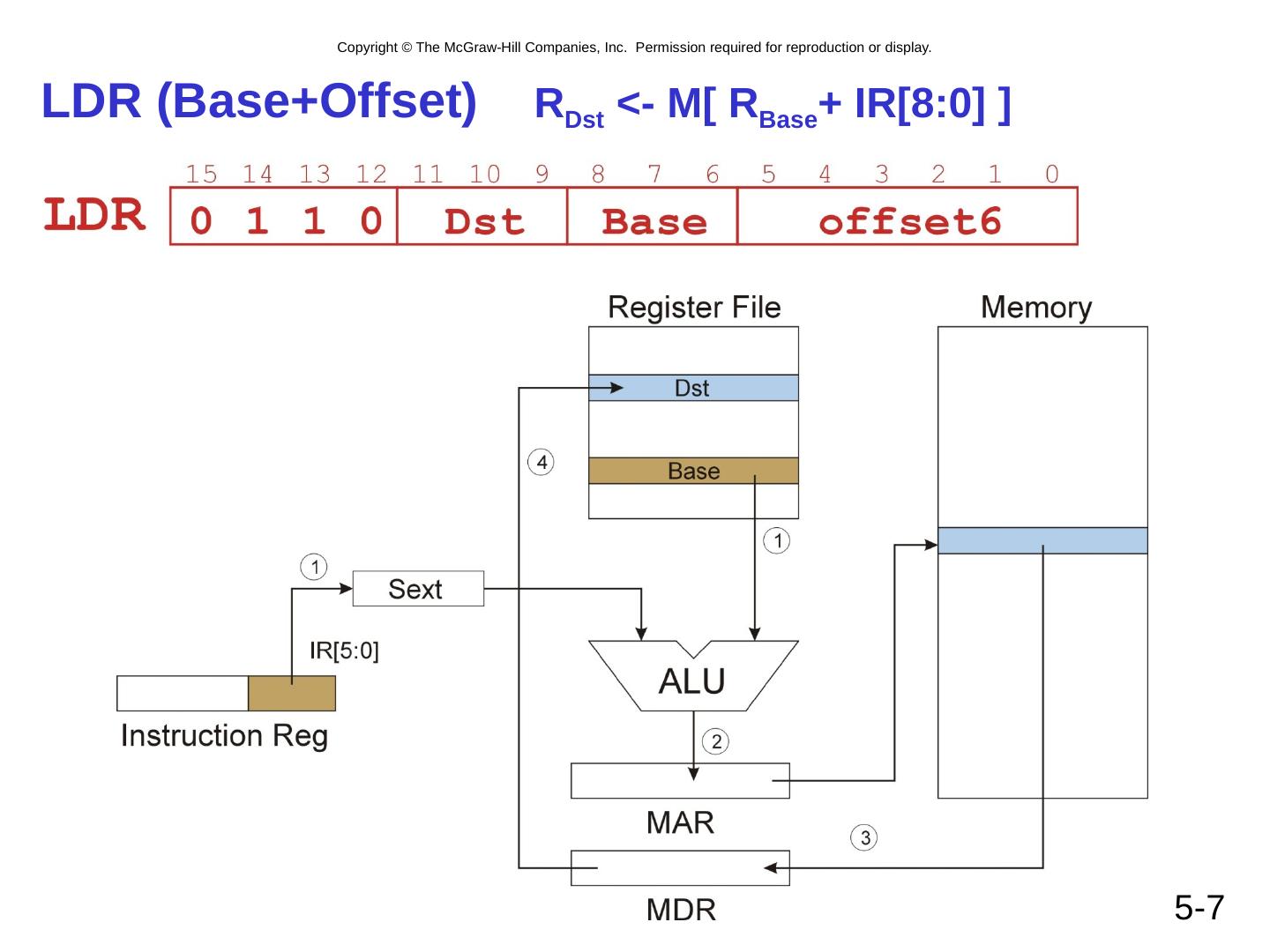

7 .5- 7 LDR ( Base+Offset ) R Dst <- M[ R Base + IR[8:0 ] ]

8 .5- 8 STR ( Base+Offset ) M [ R Base + IR[8:0] ] <- R Dst

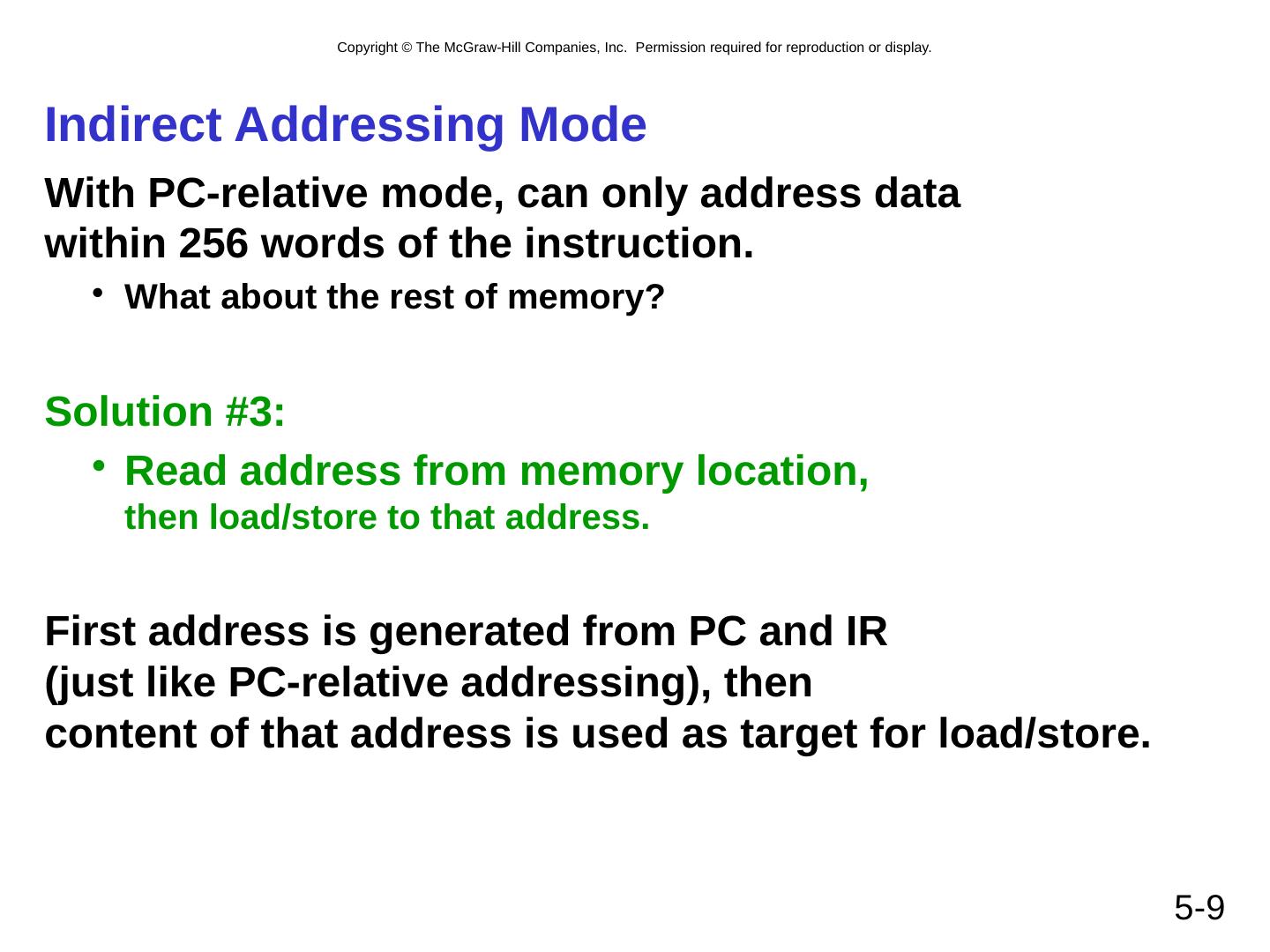

9 .5- 9 Indirect Addressing Mode With PC-relative mode, can only address data within 256 words of the instruction. What about the rest of memory? Solution #3: Read address from memory location, then load/store to that address. First address is generated from PC and IR (just like PC-relative addressing), then content of that address is used as target for load/store.

10 .5- 10 LDI (Indirect ) R Dst <- M[ M[ PC + IR[8:0 ] ] ]

11 .5- 11 STI (Indirect ) M [ M[ PC + IR[8:0] ] ] <- R Dst

12 .5- 12 Load Effective Address Computes address like PC-relative (PC plus signed offset) and stores the result into a register . Note: The address is stored in the register, not the contents of the memory location.

13 .5- 13 LEA (Immediate ) R Dst <- PC + IR[8:0]

14 .5- 14 LC-3 Data Path Revisited Filled arrow = info to be processed. Unfilled arrow = control signal.

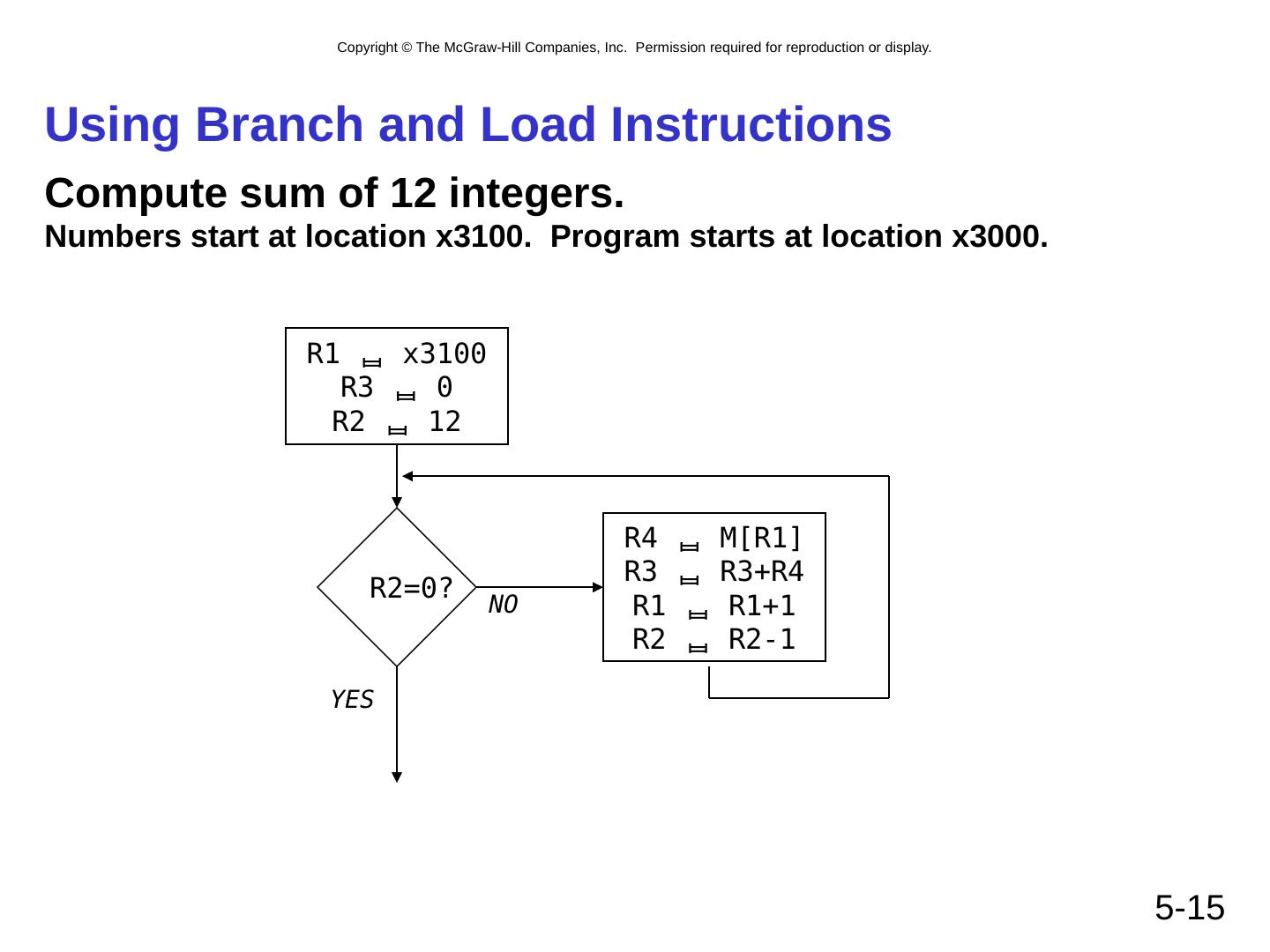

15 .5- 15 Using Branch and Load Instructions Compute sum of 12 integers. Numbers start at location x3100. Program starts at location x3000. R1 x3100 R3 0 R2 12 R2=0? R4 M[R1] R3 R3+R4 R1 R1+1 R2 R2-1 NO YES

16 .5- 16 Sample Program Address Instruction Comments x3000 1 1 1 0 0 0 1 0 1 1 1 1 1 1 1 1 R1 x3100 (PC+0xFF) x3001 0 1 0 1 0 1 1 0 1 1 1 0 0 0 0 0 R3 0 x3002 0 1 0 1 0 1 0 0 1 0 1 0 0 0 0 0 R2 0 x3003 0 0 0 1 0 1 0 0 1 0 1 0 1 1 0 0 R2 12 x3004 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 1 If Z, goto x300A (PC+5) x3005 0 1 1 0 1 0 0 0 0 1 0 0 0 0 0 0 Load next value to R4 x3006 0 0 0 1 0 1 1 0 1 1 0 0 0 0 0 1 Add to R3 x3007 0 0 0 1 0 0 1 0 0 1 1 0 0 0 0 1 Increment R1 (pointer) X3008 0 0 0 1 0 1 0 0 1 0 1 1 1 1 1 1 Decrement R2 (counter) x3009 0 0 0 0 1 1 1 1 1 1 1 1 1 0 1 0 Goto x3004 (PC-6)