- 快召唤伙伴们来围观吧

- 微博 QQ QQ空间 贴吧

- 文档嵌入链接

- <iframe src="https://www.slidestalk.com/u231/RISCV_data?embed" frame border="0" width="640" height="360" scrolling="no" allowfullscreen="true">复制

- 微信扫一扫分享

RISC-V指令格式

展开查看详情

1 .CS 61C: Great Ideas in Computer Architecture RISC-V Instruction Formats Instructors: Krste Asanović and Randy H. Katz http://inst.eecs.Berkeley.edu/~cs61c/fa17 9/14/17 Fall 2017 - Lecture #7 1

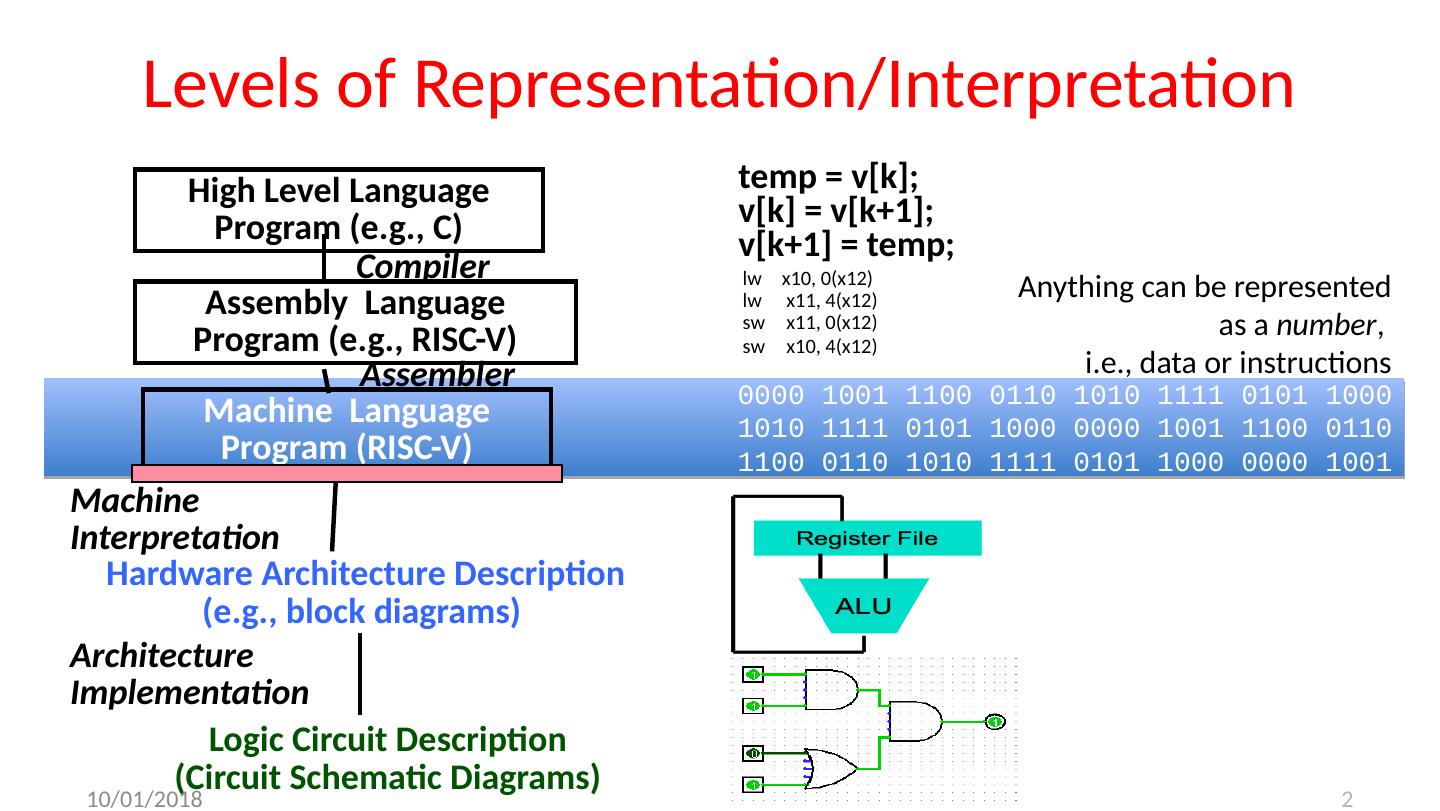

2 .Levels of Representation/Interpretation lw x10 , 0 (x12 ) lw x11 , 4 (x12 ) sw x11 , 0(x12 ) sw x10 , 4 (x12 ) High Level Language Program (e.g., C) Assembly Language Program ( e.g., RISC-V) Machine Language Program (RISC-V) Hardware Architecture Description ( e.g., block diagrams) Compiler Assembler Machine Interpretation temp = v[k ]; v[k ] = v[k+1]; v[k+1] = temp; 0000 1001 1100 0110 1010 1111 0101 1000 1010 1111 0101 1000 0000 1001 1100 0110 1100 0110 1010 1111 0101 1000 0000 1001 0101 1000 0000 1001 1100 0110 1010 1111 Architecture Implementation Anything can be represented as a number , i.e., data or instructions Logic Circuit Description (Circuit Schematic Diagrams) 9/14/17 2

3 .ENIAC ( U.Penn ., 1946) First Electronic General-Purpose Computer 3 Blazingly fast (multiply in 2.8ms!) 10 decimal digits x 10 decimal digits But needed 2-3 days to setup new program, as programmed with patch cords and switches 9/14/17 3

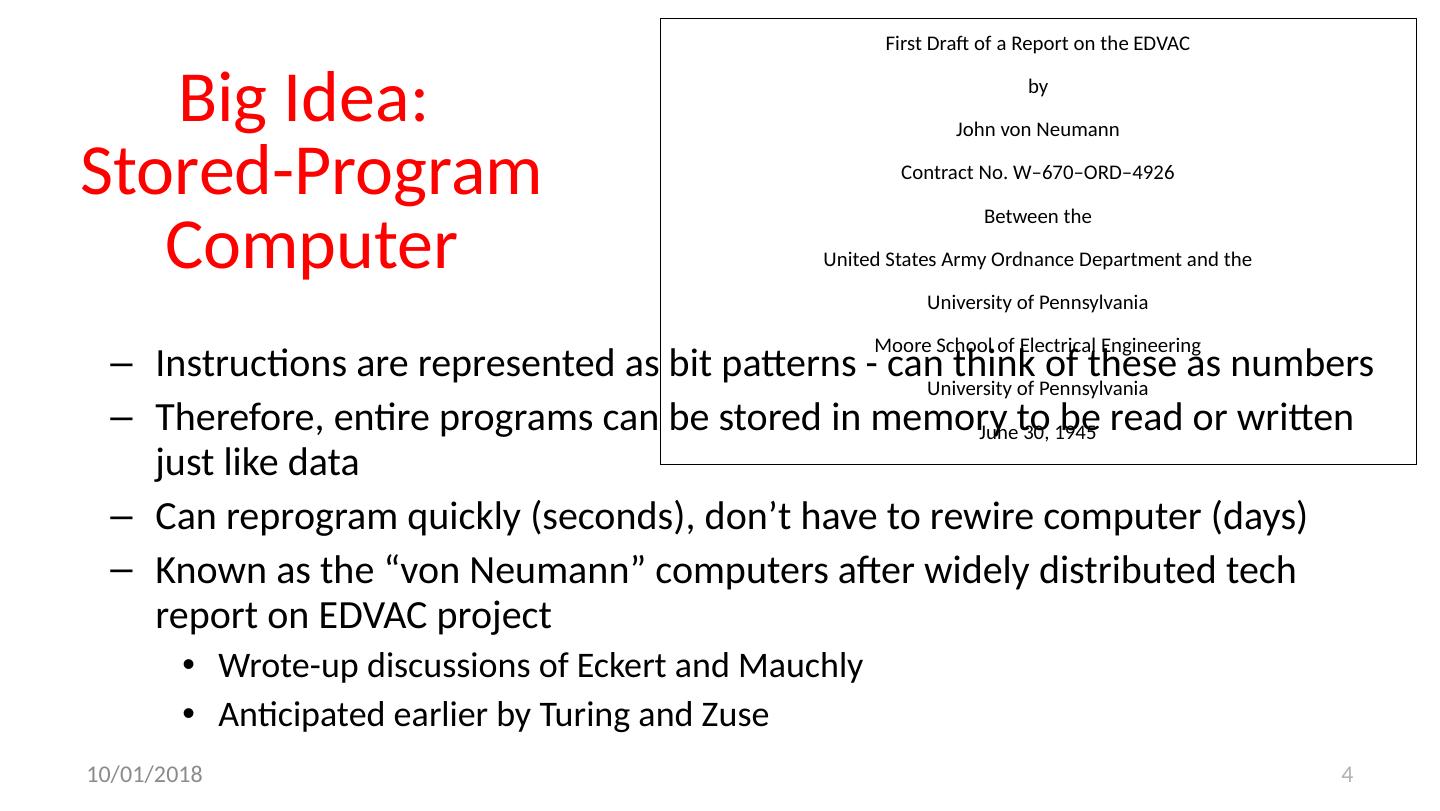

4 .Big Idea: Stored-Program Computer Instructions are represented as bit patterns - can think of these as numbers Therefore, entire programs can be stored in memory to be read or written just like data Can reprogram quickly (seconds), don’t have to rewire computer (days) Known as the “von Neumann” computers after widely distributed tech report on EDVAC project Wrote-up discussions of Eckert and Mauchly Anticipated earlier by Turing and Zuse First Draft of a Report on the EDVAC by John von Neumann Contract No. W–670–ORD– 4926 Between the United States Army Ordnance Department and the University of Pennsylvania Moore School of Electrical Engineering University of Pennsylvania June 30, 1945 9/14/17 4

5 .EDSAC (Cambridge, 1949) First General Stored-Program Computer Programs held as numbers in memory 35-bit binary 2’s complement words 9/14/17 5

6 .Consequence #1: Everything Has a Memory Address Since all instructions and data are stored in memory, everything has a memory address: instructions, data words B oth branches and jumps use these C pointers are just memory addresses: they can point to anything in memory Unconstrained use of addresses can lead to nasty bugs; avoiding errors up to you in C; limited in Java by language design One register keeps address of instruction being executed: “Program Counter” (PC) Basically a pointer to memory Intel calls it Instruction Pointer (a better name) 6 9/14/17

7 .Consequence #2: Binary Compatibility Programs are distributed in binary form Programs bound to specific instruction set Different version for phones and PC s New machines want to run old programs (“binaries”) as well as programs compiled to new instructions Leads to “backward-compatible” instruction set evolving over time Selection of Intel 8088 in 1981 for 1 st IBM PC is major reason latest PCs still use 80x86 instruction set; could still run program from 1981 PC today 7 9/14/17

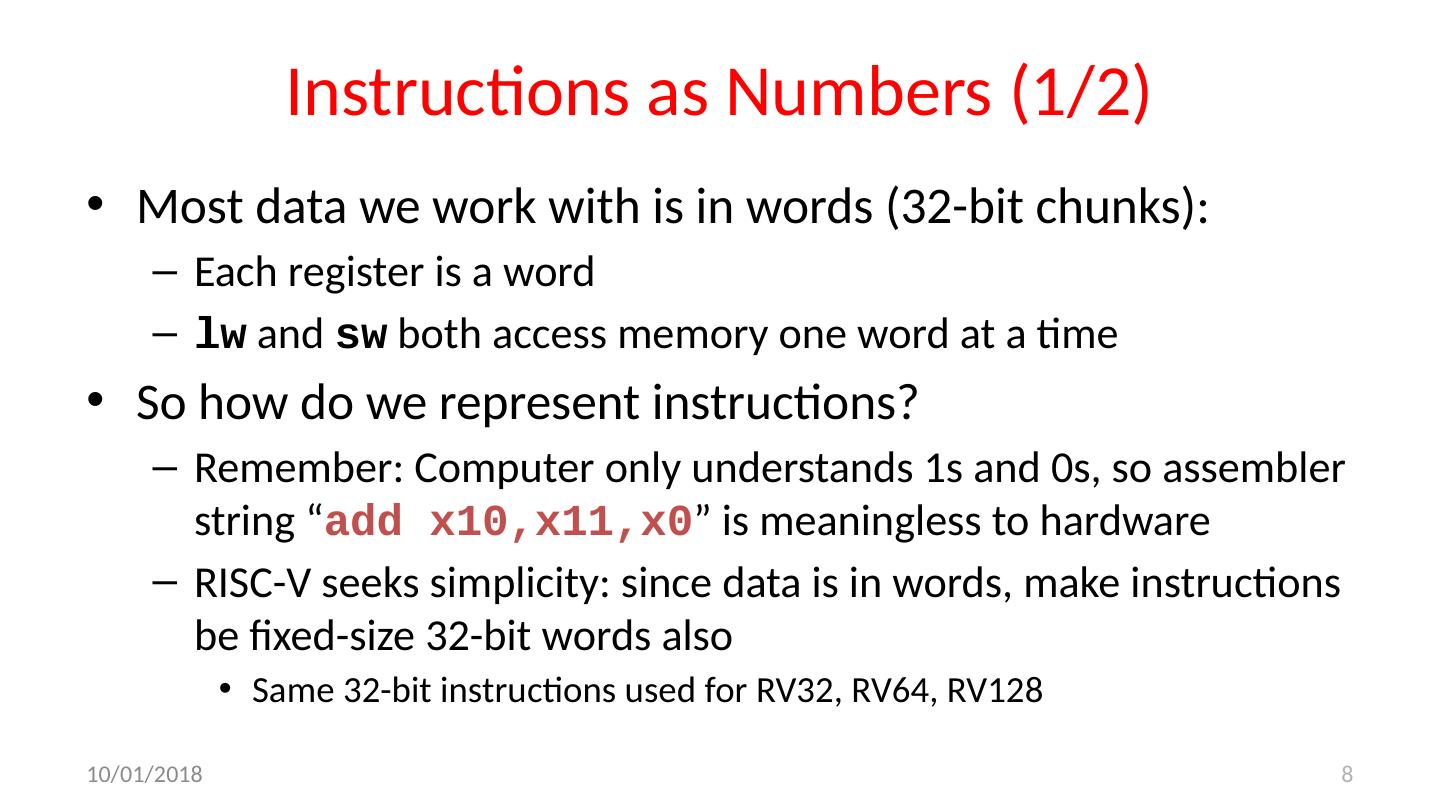

8 .Instructions as Numbers (1/2) Most data we work with is in words (32-bit chunks): Each register is a word lw and sw both access memory one word at a time So how do we represent instructions? Remember: Computer only understands 1s and 0s, so assembler string “ add x10,x11,x0 ” is meaningless to hardware RISC-V seeks simplicity: since data is in words, make instructions be fixed-size 32-bit words also Same 32-bit instructions used for RV32, RV64, RV128 8 9/14/17

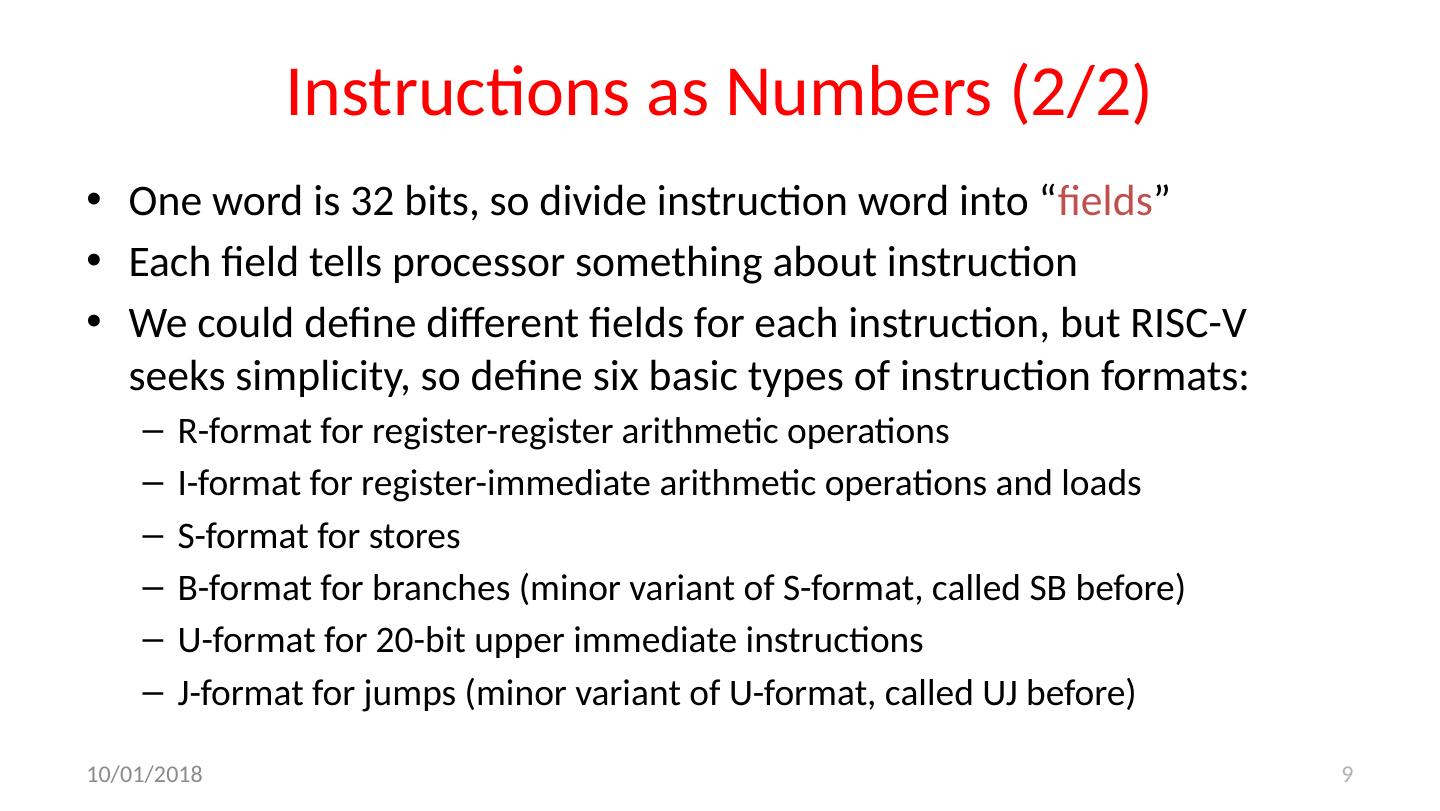

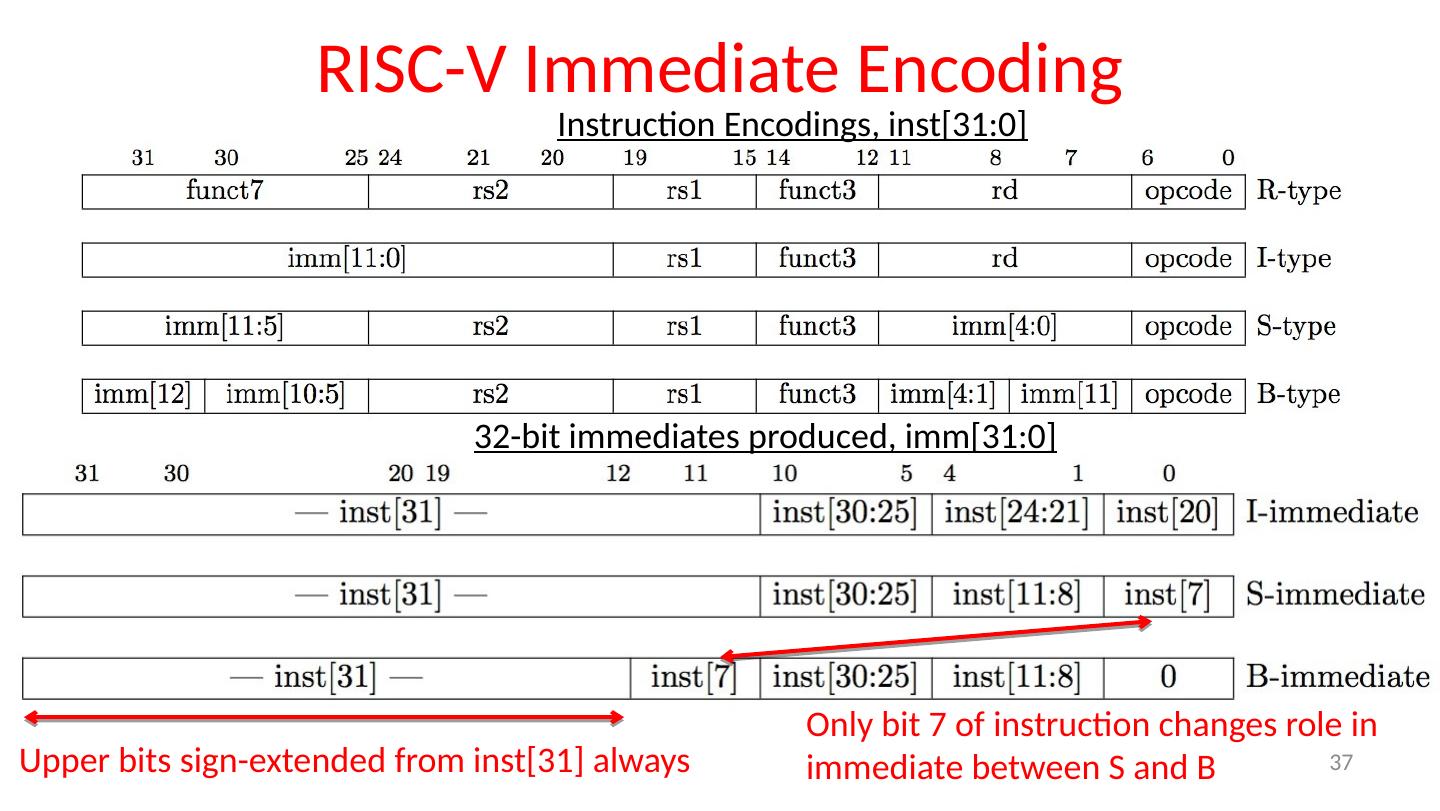

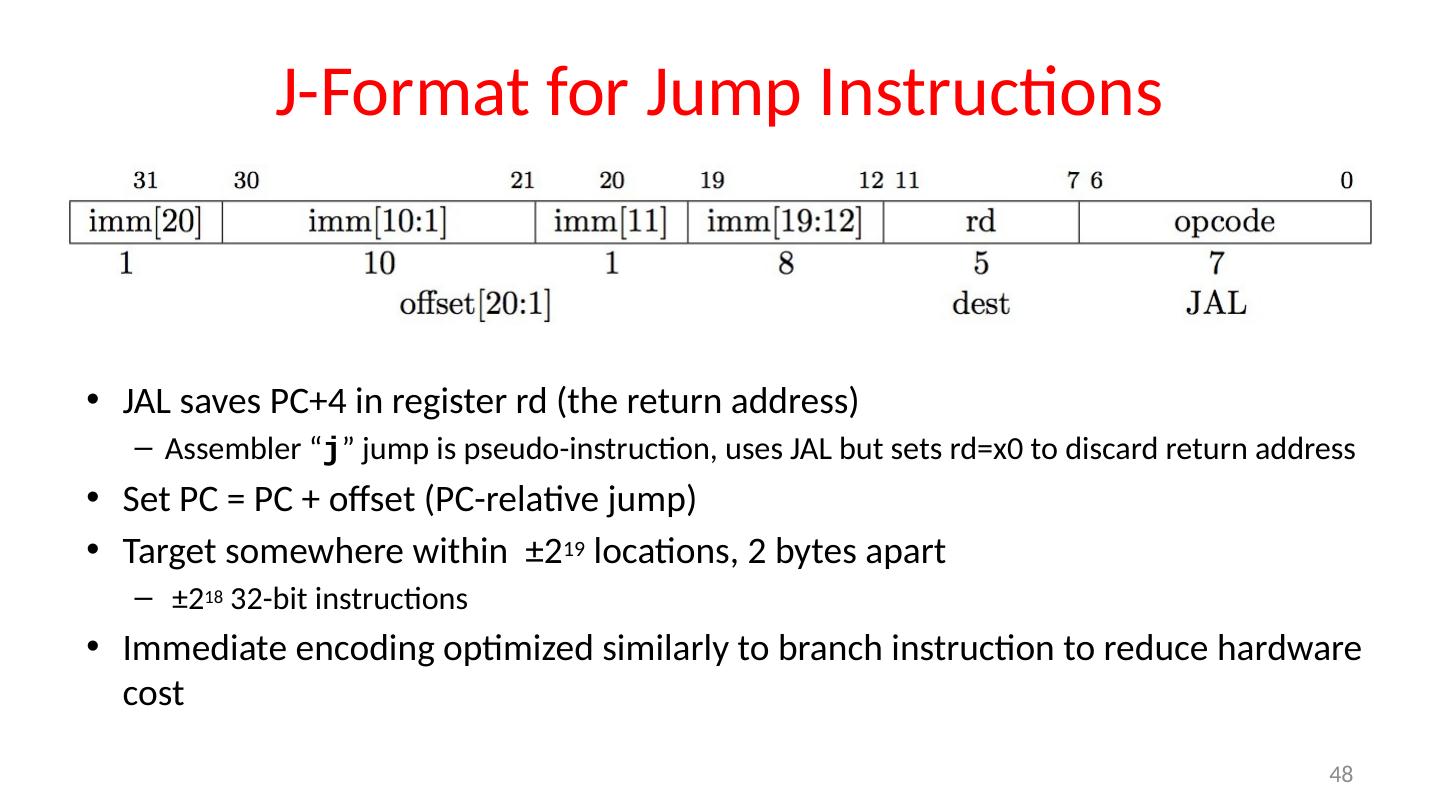

9 .Instructions as Numbers (2/2) One word is 32 bits, so divide instruction word into “ fields ” Each field tells processor something about instruction We could define different fields for each instruction, but RISC-V seeks simplicity, so define six basic types of instruction formats: R-format for register-register arithmetic operations I-format for register-immediate arithmetic operations and loads S -format for stores B-format for branches (minor variant of S-format, called SB before) U-format for 20-bit upper immediate instructions J-format for jumps (minor variant of U- format, called UJ before) 9/14/17 9

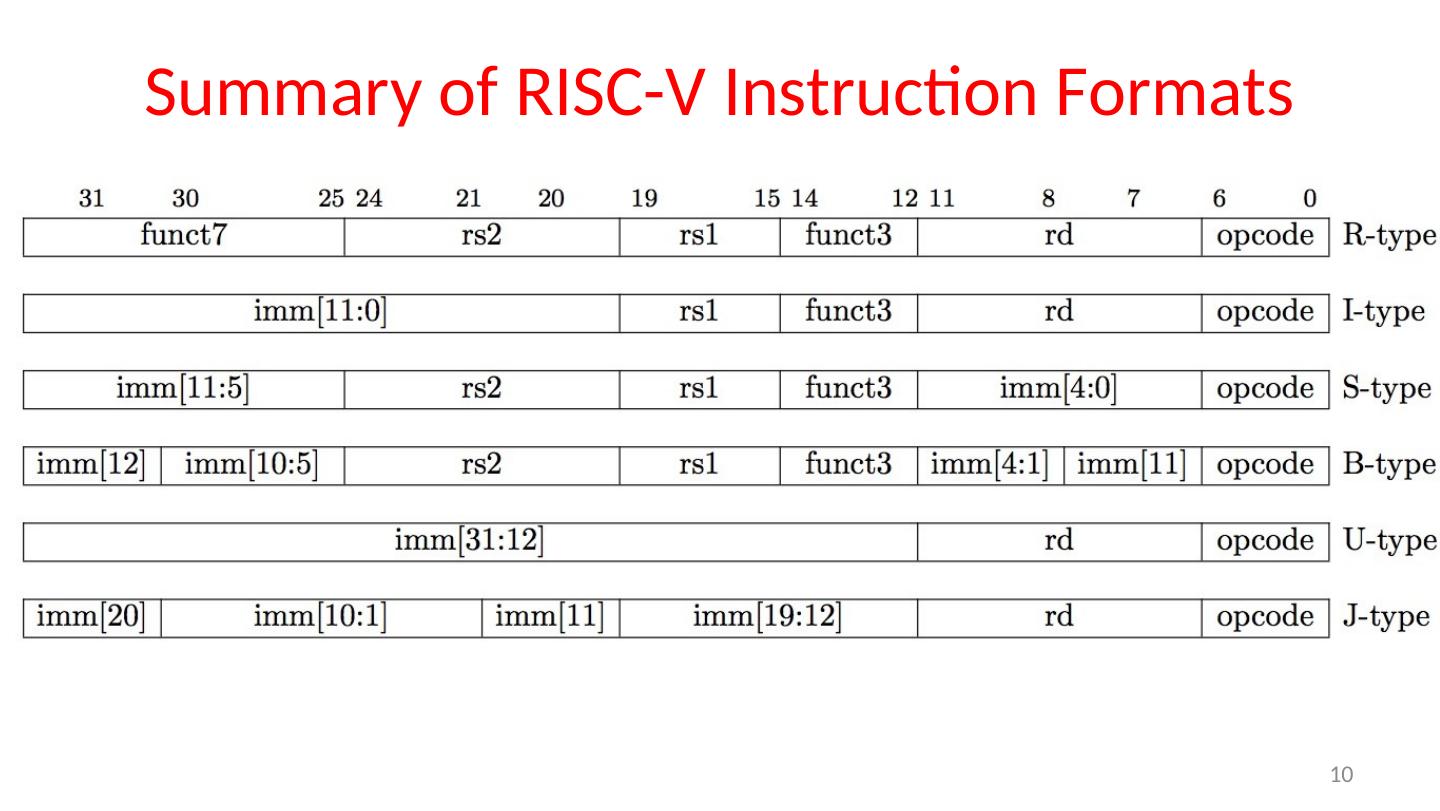

10 .Summary of RISC-V Instruction Formats 10

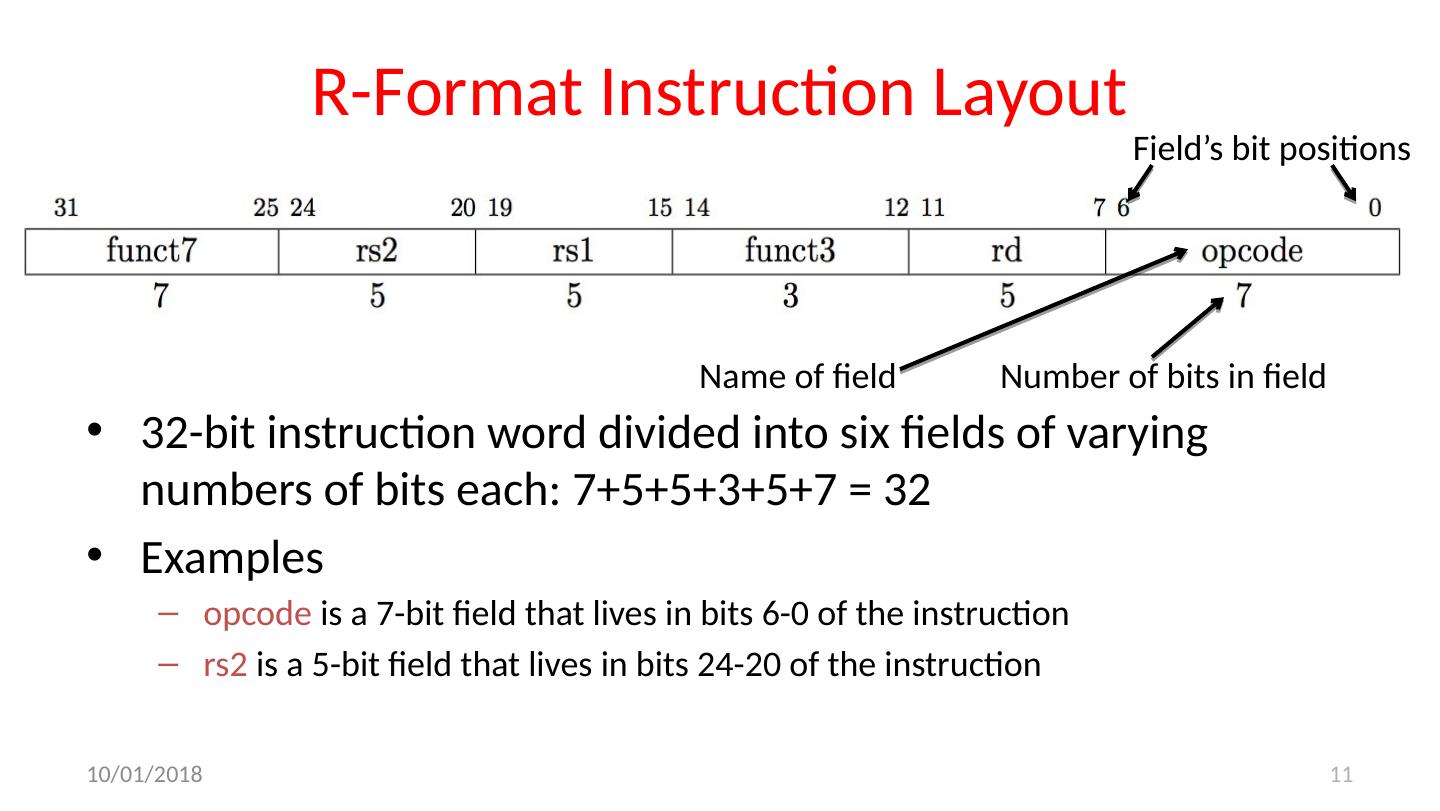

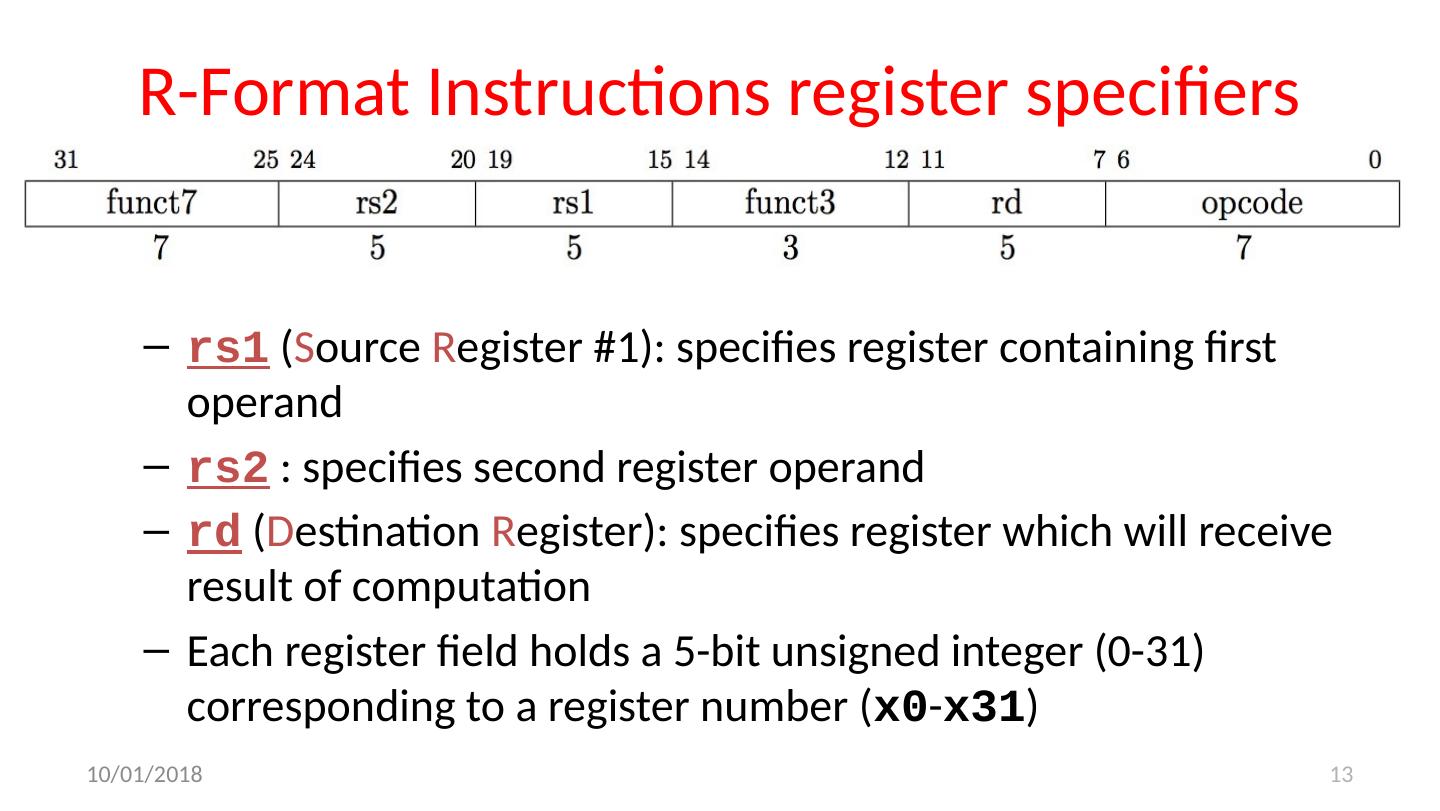

11 .R-Format Instruction Layout 32-bit instruction word divided into six fields of varying numbers of bits each: 7+5+5+3+5+7 = 32 Examples opcode is a 7-bit field that lives in bits 6-0 of the instruction rs2 is a 5- bit field that lives in bits 24-20 of the instruction 11 9/14/17 Field’s bit positions Number of bits in field Name of field

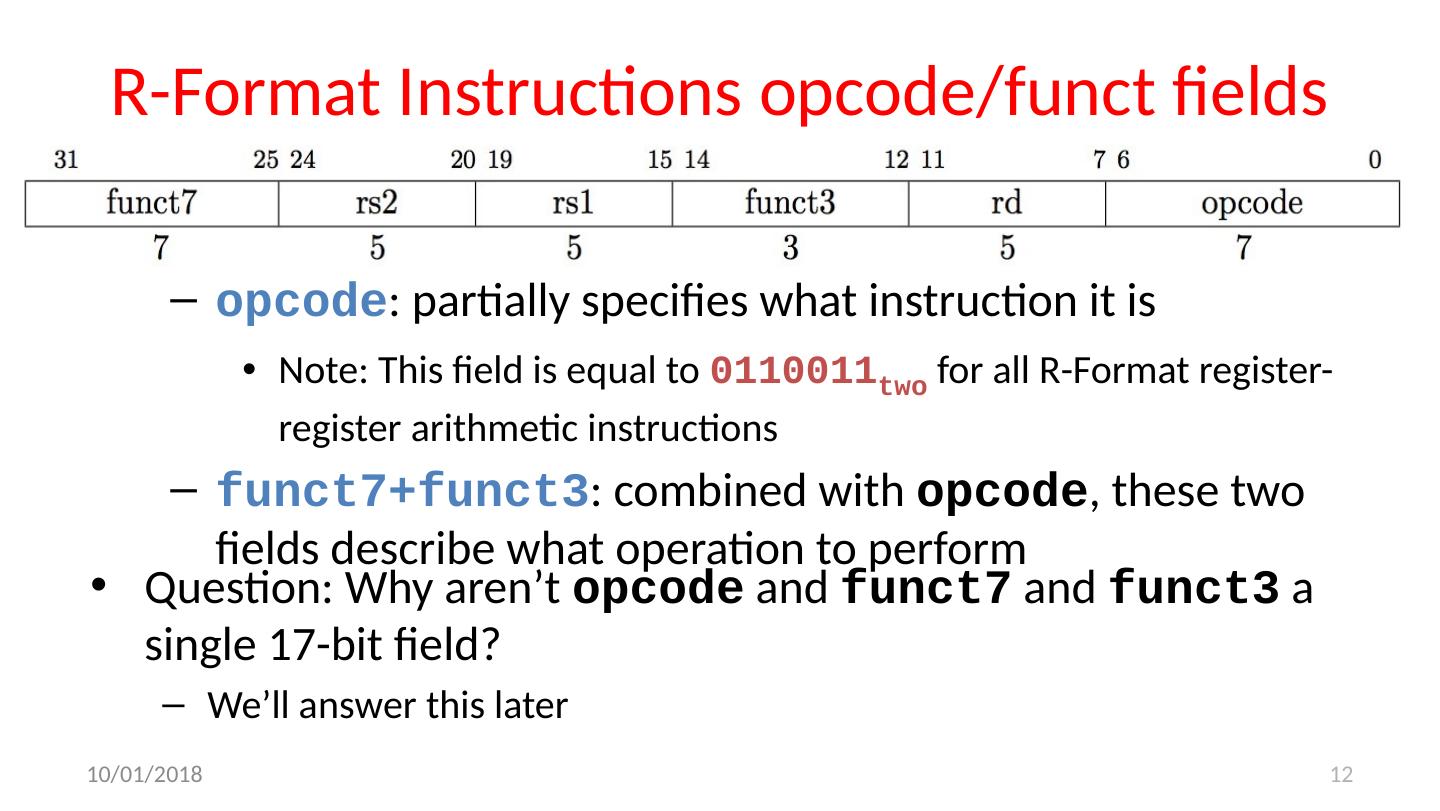

12 .R-Format Instructions opcode / funct fields opcode : partially specifies what instruction it is Note: This field is equal to 0110011 two for all R-Format register-register arithmetic instructions funct7+funct3 : combined with opcode , these two fields describe what operation to perform 12 Question: Why aren’t opcode and funct7 and funct3 a single 17-bit field? We’ll answer this later 9/14/17

13 .R-Format Instructions register specifiers rs1 ( S ource R egister #1) : specifies register containing first operand rs2 : specifies second register operand rd ( D estination R egister): specifies register which will receive result of computation Each register field holds a 5-bit unsigned integer ( 0- 31) corresponding to a register number ( x0 - x31 ) 13 9/14/17

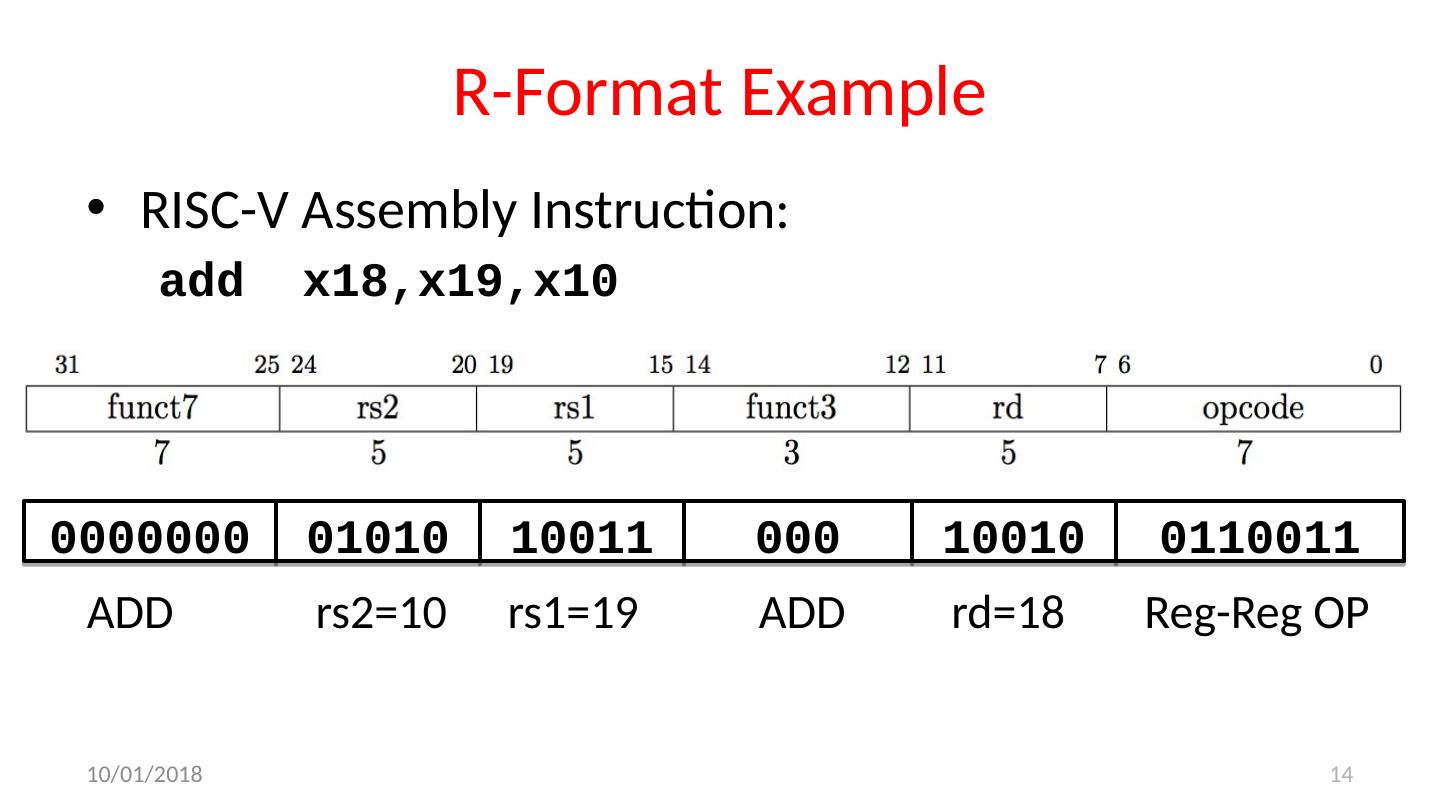

14 .R-Format Example RISC-V Assembly Instruction: add x18,x19,x10 14 9/14/17 0000000 01010 1 0 011 000 10010 0110011 Reg-Reg OP r d =18 ADD ADD r s2=10 rs1=19

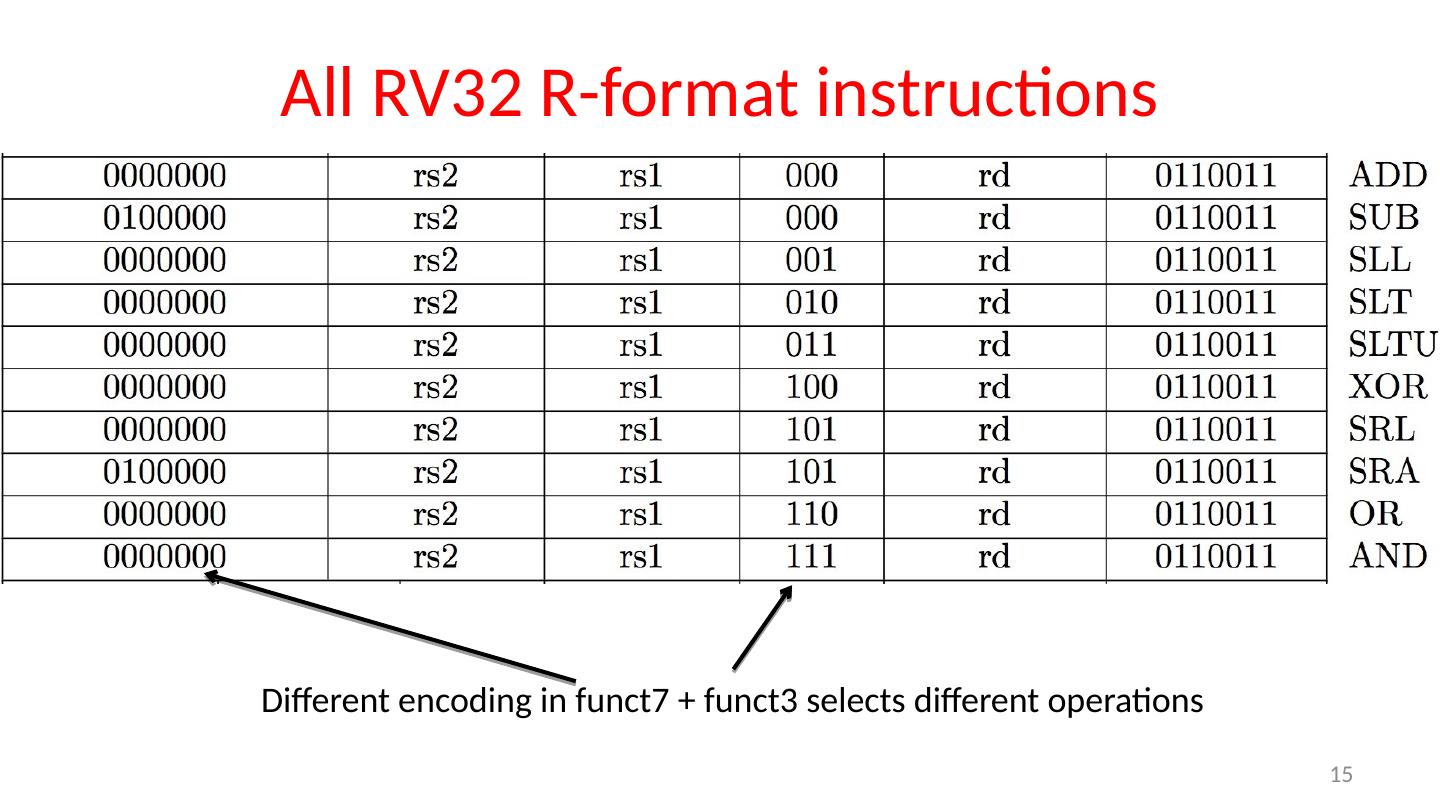

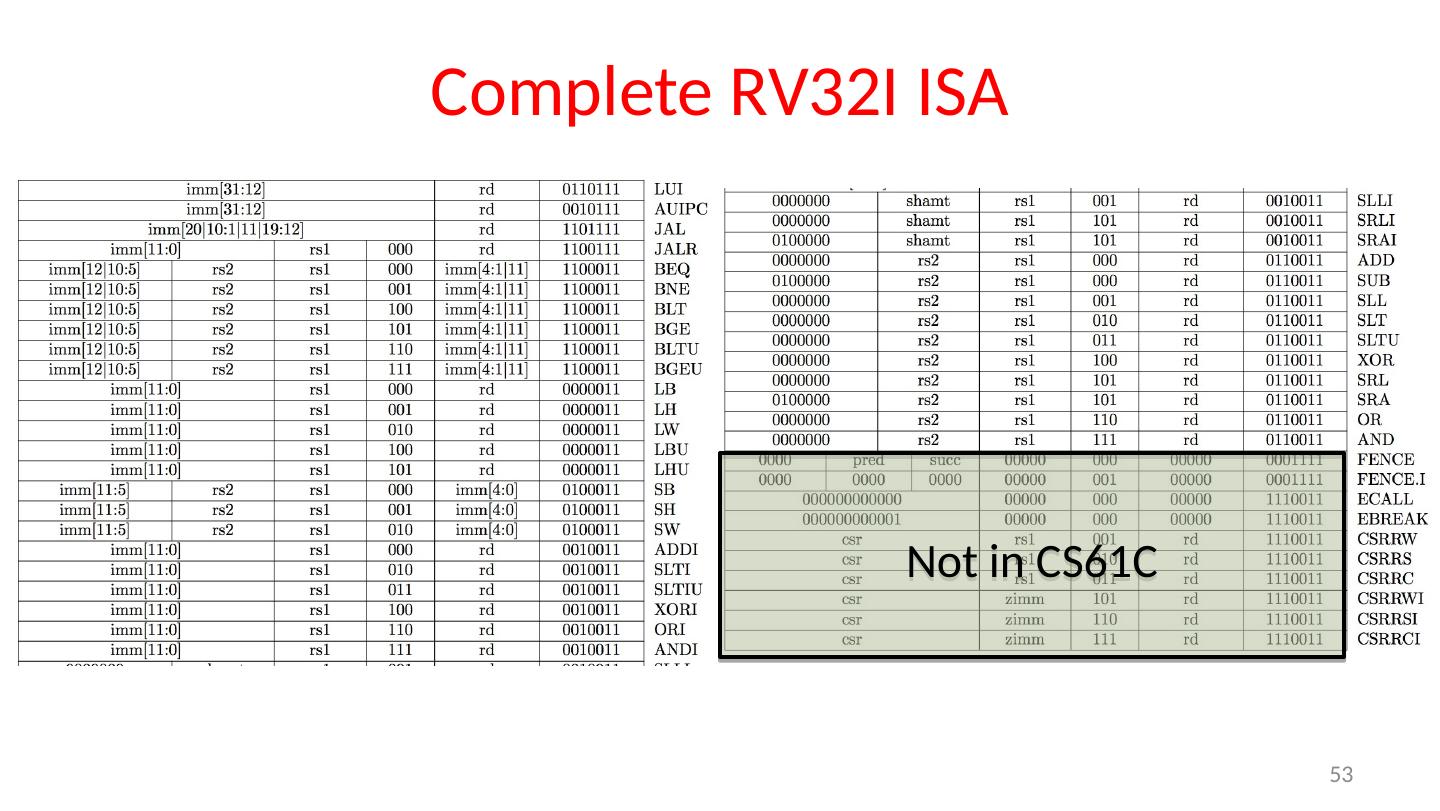

15 .All RV32 R-format instructions 15 Different encoding in funct7 + funct3 selects different operations

16 .I-Format Instructions What about instructions with immediates ? 5-bit field only represents numbers up to the value 31: immediates may be much larger than this Ideally, RISC-V would have only one instruction format (for simplicity): unfortunately, we need to compromise Define new instruction format that is mostly consistent with R-format Notice if instruction has immediate, then uses at most 2 registers (one source, one destination) 9/14/17 16

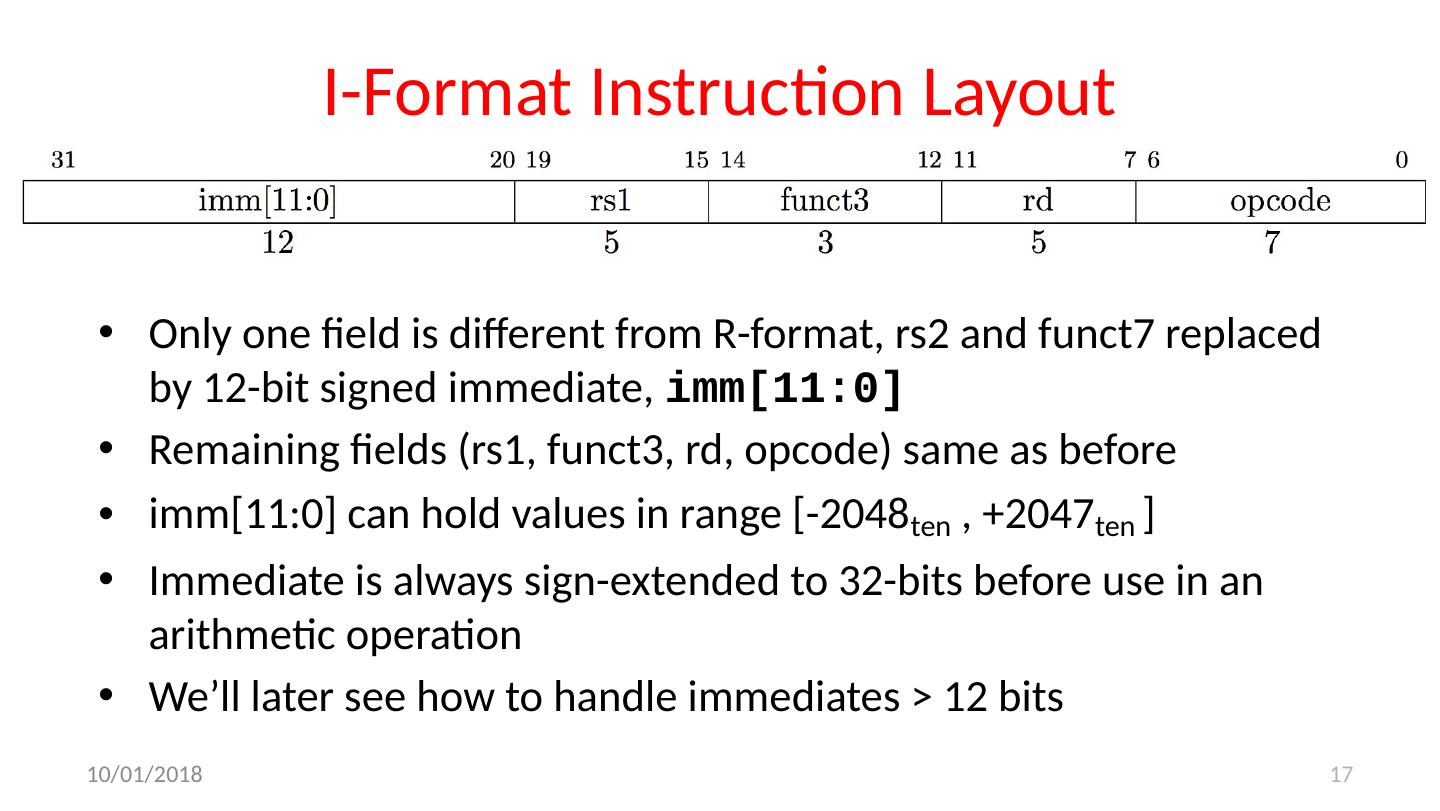

17 .I -Format Instruction Layout 17 9/14/17 Only one field is different from R- format, rs2 and funct7 replaced by 12-bit signed immediate, imm [11:0] Remaining fields (rs1, funct3, rd , opcode ) same as before i mm [11:0] can hold values in range [-2048 ten , +2047 ten ] Immediate is always sign-extended to 32-bits before use in an arithmetic operation W e’ll later see how to handle immediates > 12 bits

18 .I -Format Example RISC-V Assembly Instruction: addi x15,x1,-50 18 9/14/17 111111001110 00001 000 01111 0010011 OP- Imm r d =15 ADD i mm =-50 rs1=1

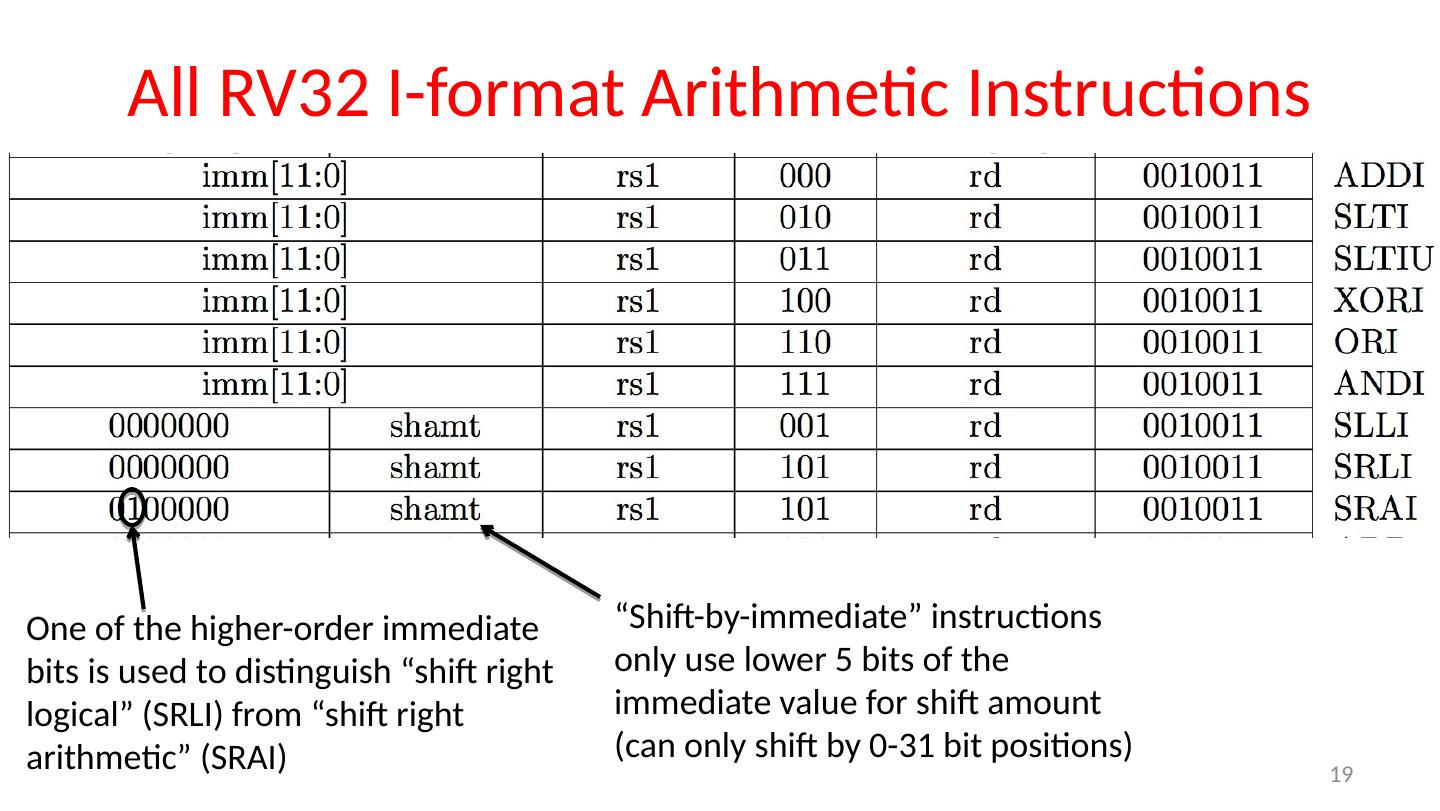

19 .All RV32 I-format Arithmetic Instructions 19 “Shift-by-immediate” instructions only use lower 5 bits of the immediate value for shift amount (can only shift by 0-31 bit positions) One of the higher-order immediate bits is used to distinguish “shift right logical” (SRLI) from “shift right arithmetic” (SRAI)

20 .Administrivia HW0 Grades were released If you have an issue with them, please fill out this form by tonight: https:// goo.gl/forms/QH44Iw746pcCxOyH2 HW1 Part 1 Due next Monday, Part 2 Due Friday Sept 22 Homework-oriented office hours next Monday (check the website) Homework Party on next Wednesday (6:30-10pm in 293 Cory) Autograded results to be released every noon starting this Friday Midterm #1 in 1.5 weeks: September 26! Two sided 8.5” x 11” cheat sheet + RISC-V Green Card that we give you DSP students: please make sure we know about your special accommodations (contact Steven Ho the head TA if you haven’t yet) 9/14/17 20

21 .Break! 9/14/17 21

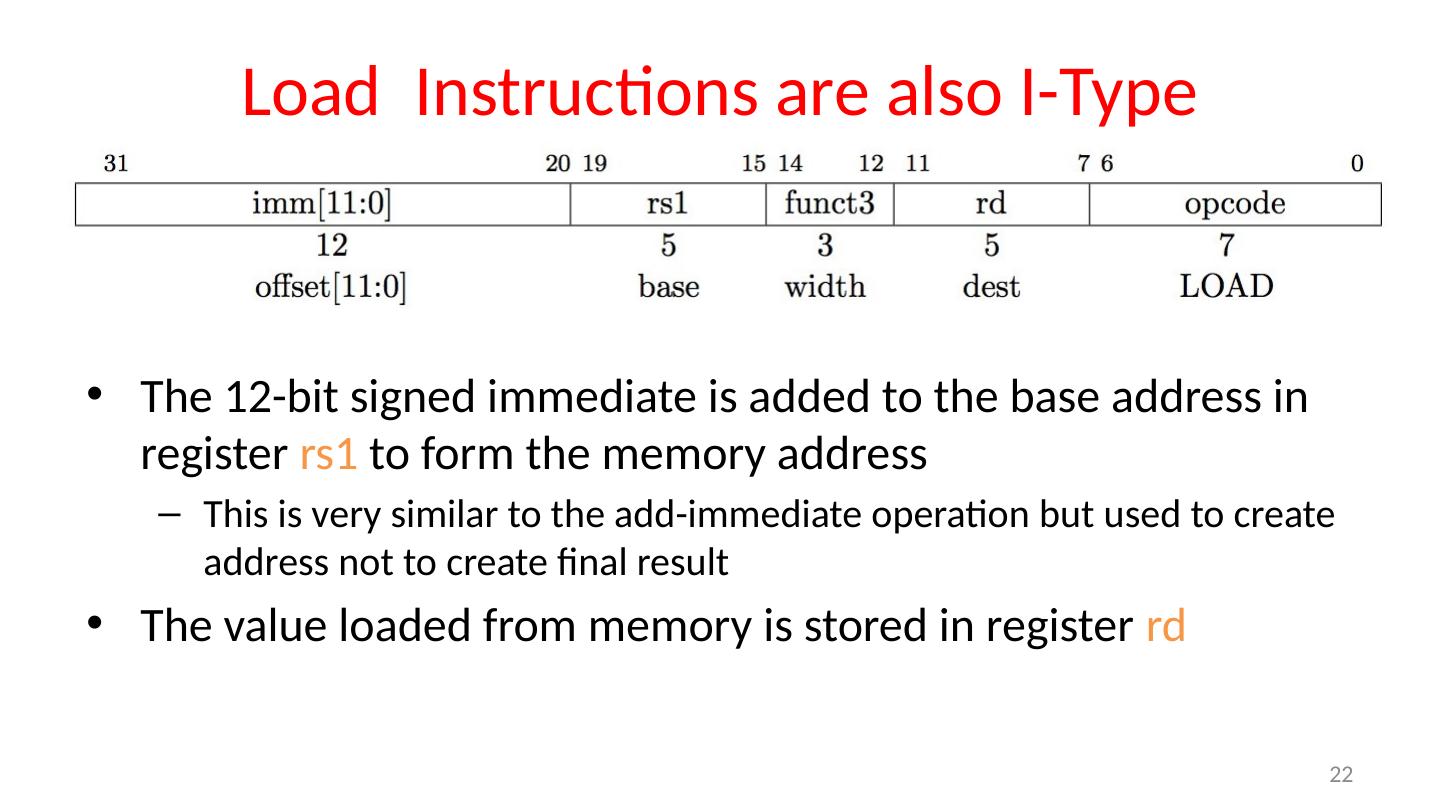

22 .Load Instructions are also I-Type 22 The 12-bit signed immediate is added to the base address in register rs1 to form the memory address This is very similar to the add-immediate operation but used to create address not to create final result The value loaded from memory is stored in register rd

23 .I -Format Load Example RISC-V Assembly Instruction: lw x14, 8(x2) 23 9/14/17 000000001000 00010 010 01110 0000011 LOAD r d =14 LW i mm =+8 rs1=2

24 .All RV32 Load Instructions LBU is “load unsigned byte” LH is “load halfword ”, which loads 16 bits (2 bytes) and sign-extends to fill destination 32-bit register LHU is “load unsigned halfword ”, which zero-extends 16 bits to fill destination 32-bit register There is no LWU in RV32, because there is no sign/zero extension needed when copying 32 bits from a memory location into a 32-bit register 24 funct3 field encodes size and signedness of load data

25 .S -Format Used for Stores 25 9/14/17 Store needs to read two registers, rs1 for base memory address, and rs2 for data to be stored, as well as need immediate offset! Can’t have both rs2 and immediate in same place as other instructions! Note that stores don’t write a value to the register file, no rd ! RISC-V design decision is move low 5 bits of immediate to where rd field was in other instructions – keep rs1/rs2 fields in same place register names more critical than immediate bits in hardware design

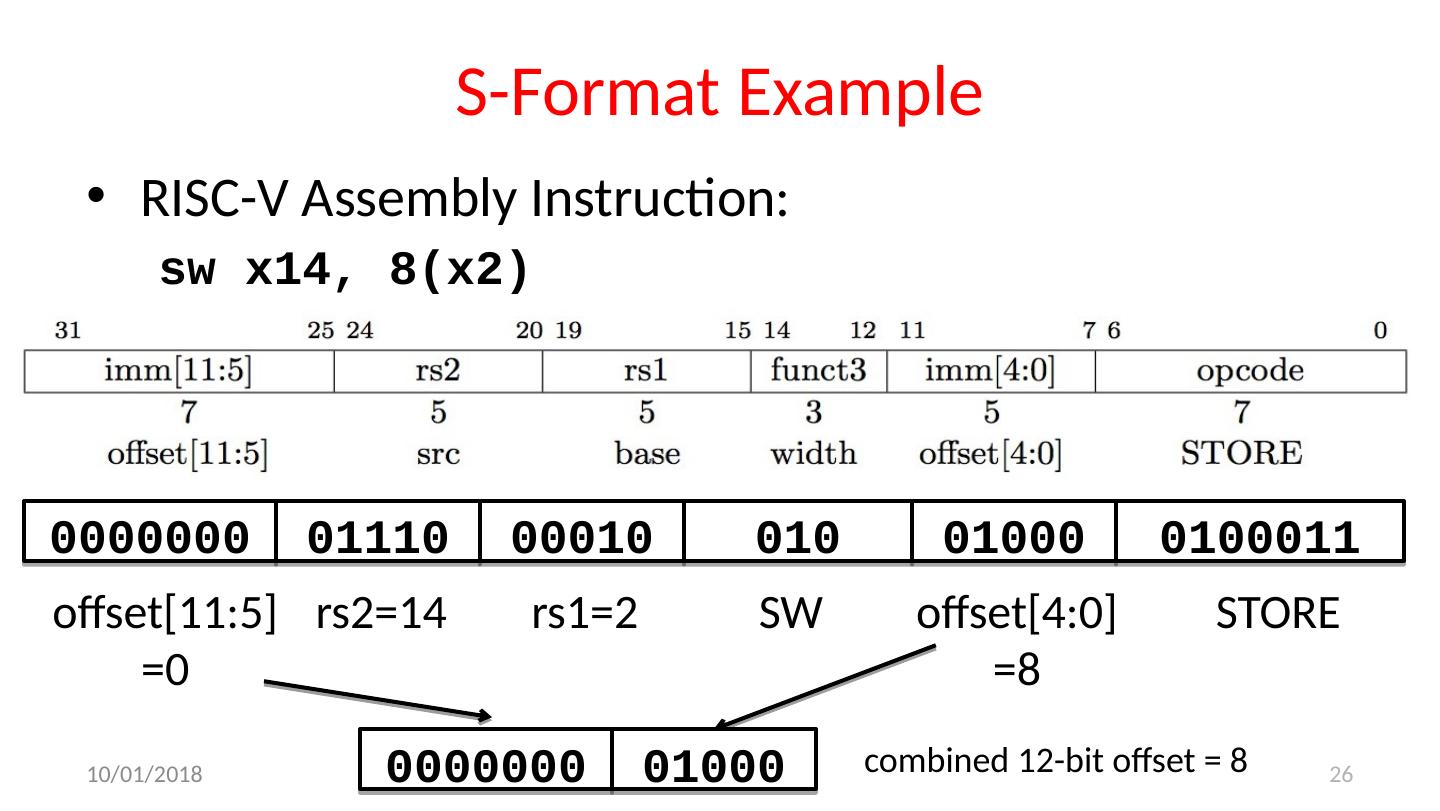

26 .S-Format Example RISC-V Assembly Instruction: s w x14, 8(x2) 26 9/14/17 0000000 01110 00010 010 01000 0100011 STORE offset[4:0] =8 SW offset[11:5] =0 r s2=14 rs1=2 combined 12-bit offset = 8 0000000 01000

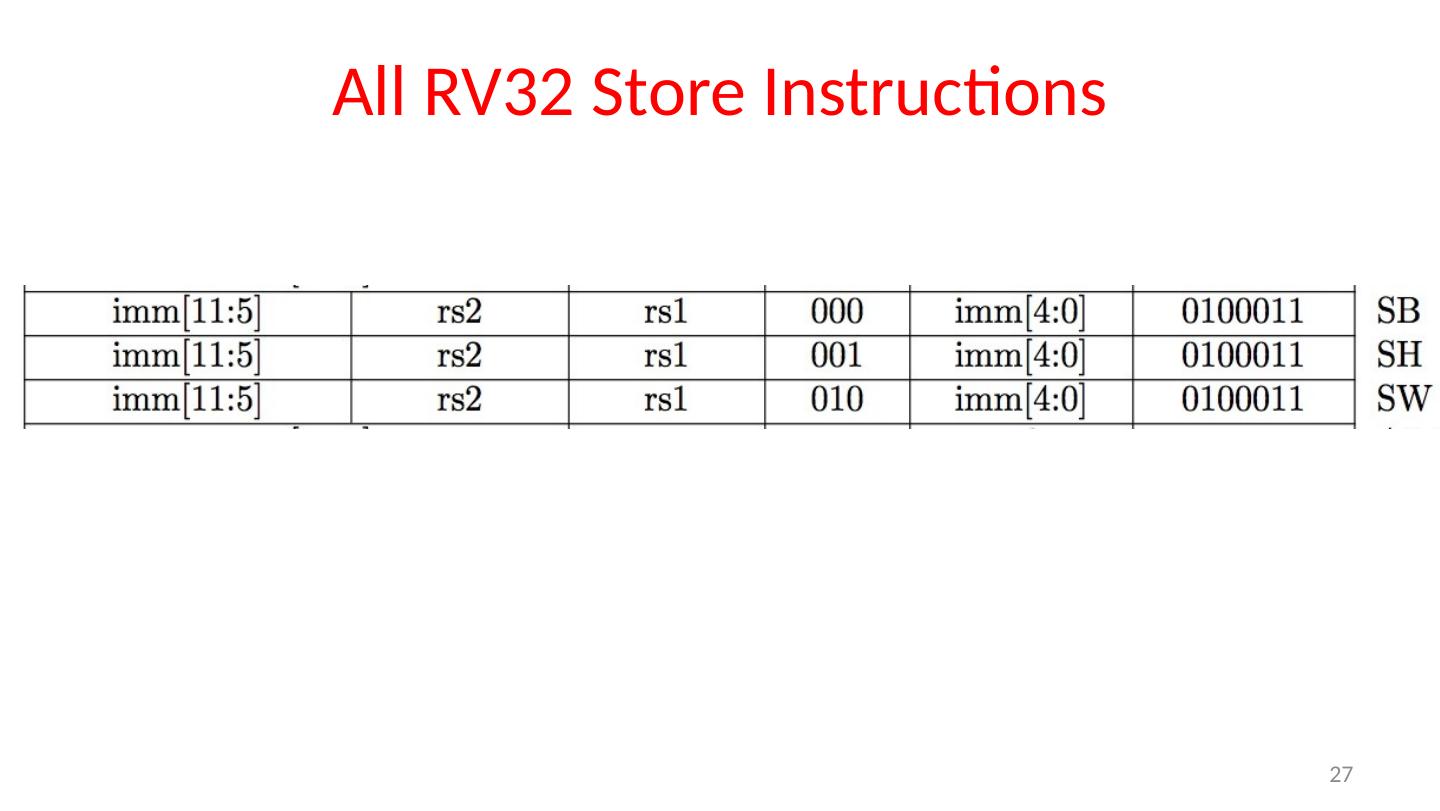

27 .All RV32 Store Instructions 27

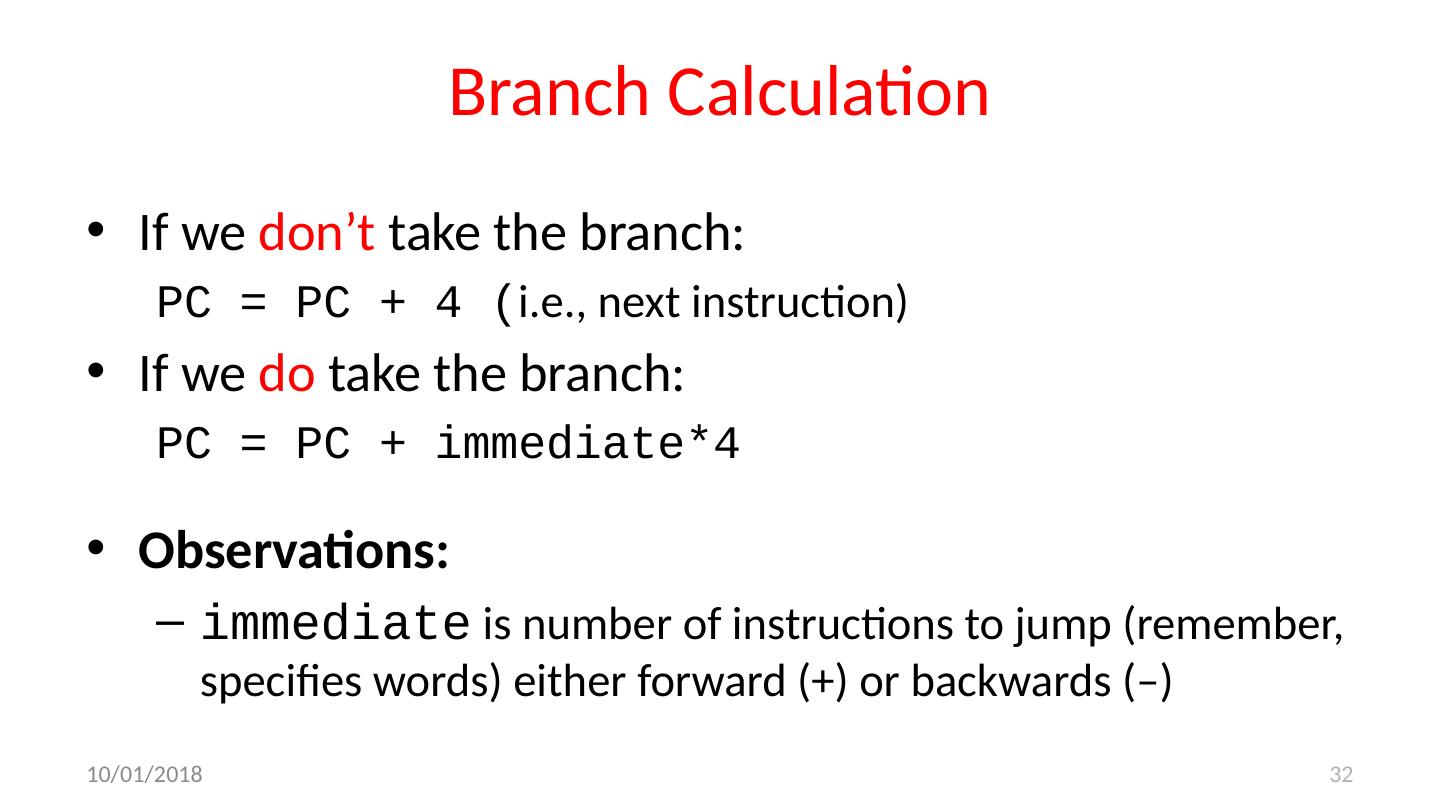

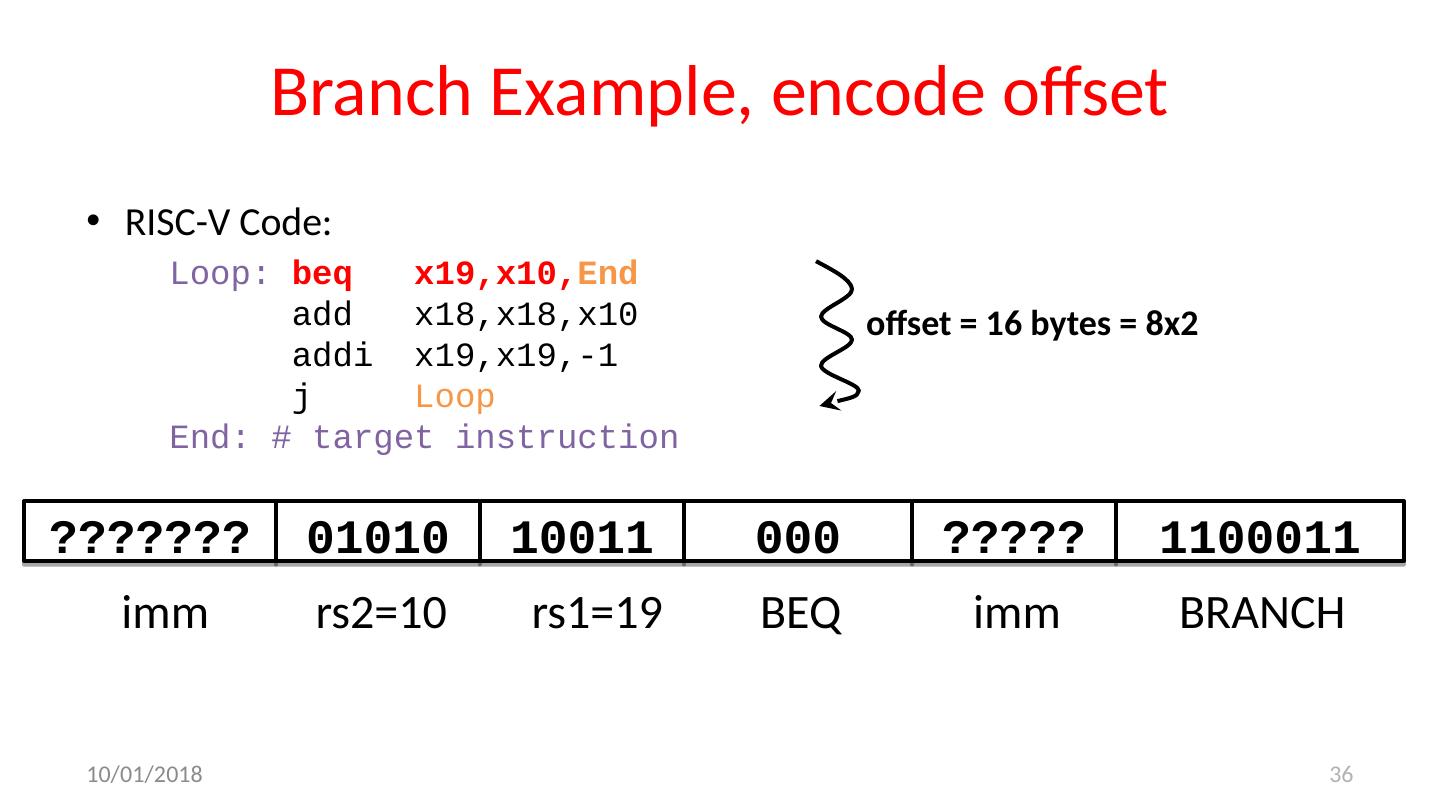

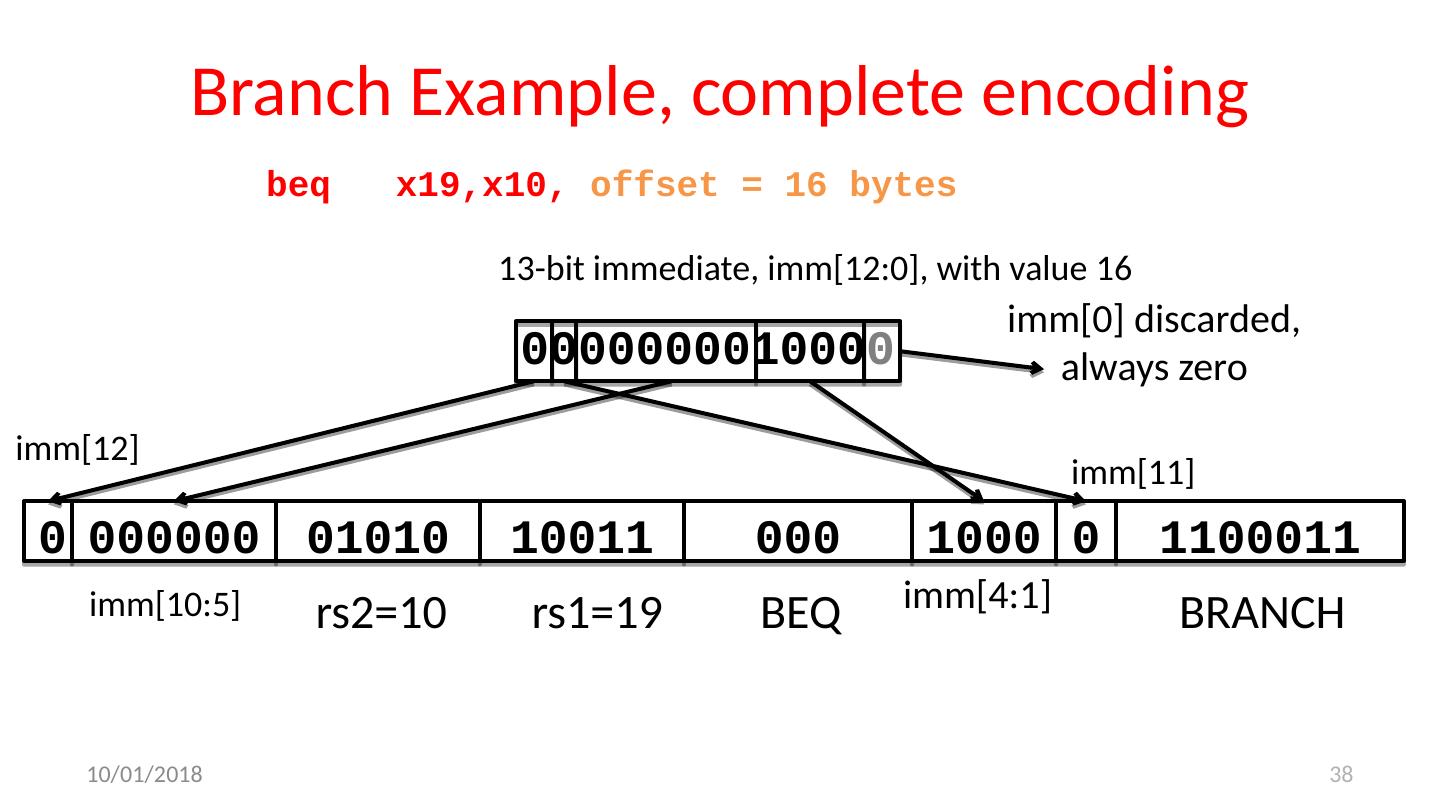

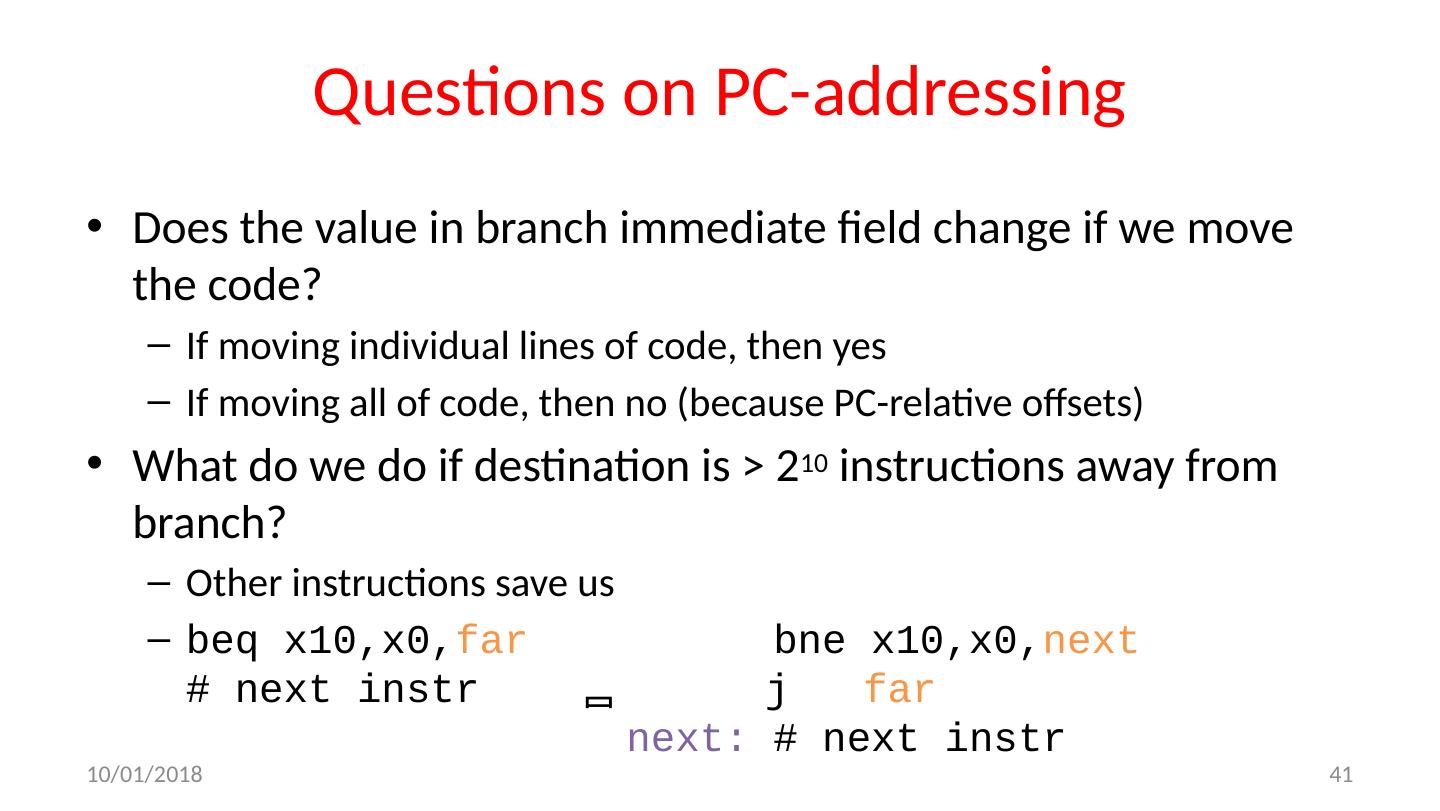

28 .RISC-V Conditional Branches E.g., BEQ x1, x2, L abel Branches read two registers but don’t write a register ( similar to stores) How to encode label, i.e., where to branch to? 28

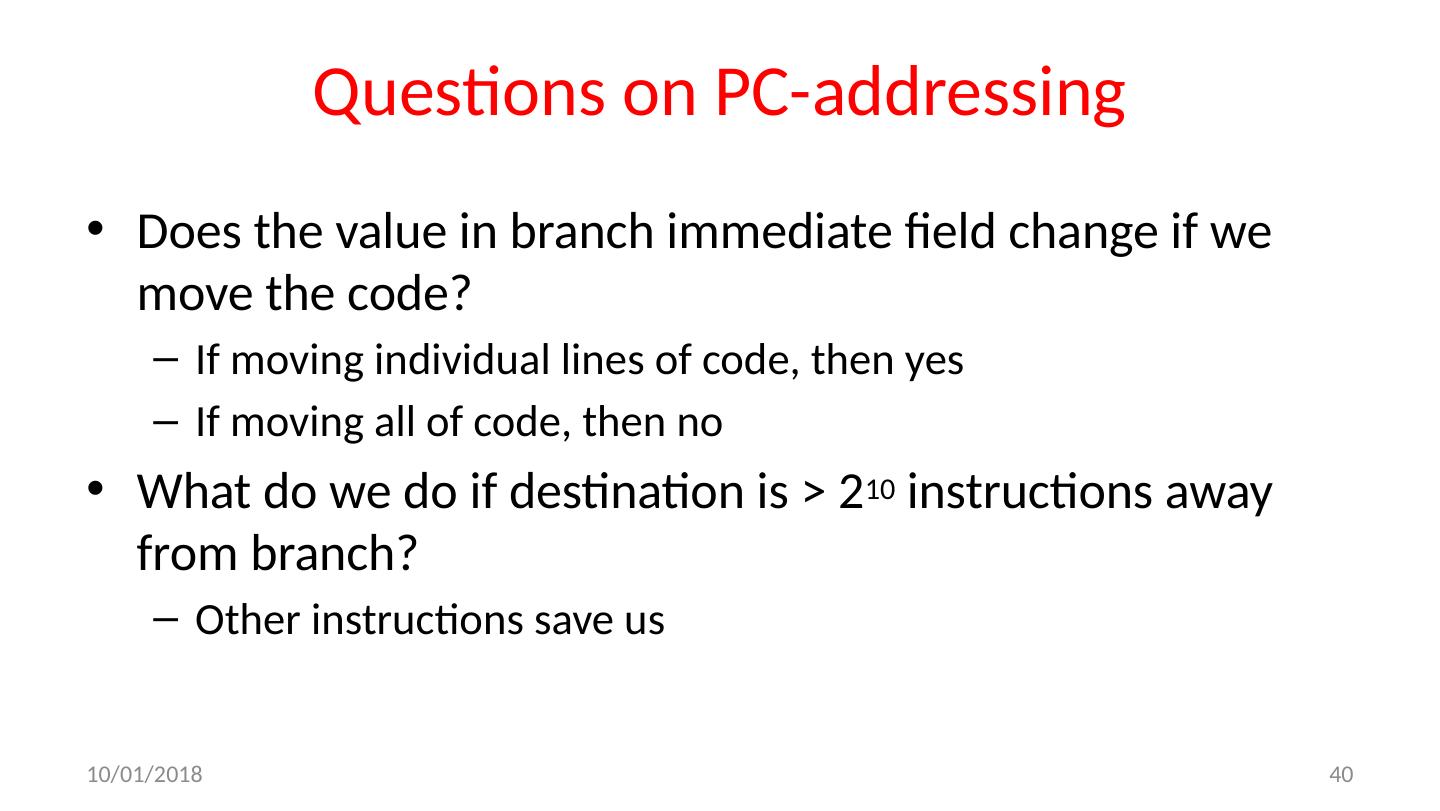

29 .Branching Instruction Usage Branches typically used for loops ( if-else , while , for ) Loops are generally small (< 50 instructions) Function calls and unconditional jumps handled with jump instructions (J-Format) Recall: Instructions stored in a localized area of memory (Code/Text) Largest branch distance limited by size of code Address of current instruction stored in the program counter (PC) 9/14/17 29