- 快召唤伙伴们来围观吧

- 微博 QQ QQ空间 贴吧

- 文档嵌入链接

- <iframe src="https://www.slidestalk.com/u6/Introduction_to_RISCV?embed" frame border="0" width="640" height="360" scrolling="no" allowfullscreen="true">复制

- 微信扫一扫分享

Introduction_to_RISC-V

- 为什么Intel不能售卖移动芯片?

– 99%+的手机和平板,是基于ARM’s v7/v8 ISA - 为什么ARM生态伙伴不能制造出服务器产品?

– 99%+的笔记本电脑/台式机和服务器芯片是基于AMD64 ISA (95%+由Intel生产) - IBM怎么还能在售卖Mainframe?

– IBM 360是最古老的ISA (50多年历史)

说到RISC-V,必须推荐一本书《RISC-V手册》

展开查看详情

1 .RISC-V Palmer Dabbelt, SiFive COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

2 . Why Instruction Set Architecture matters • Why can’t Intel sell mobile chips? – 99%+ of mobile phones/tablets are based on ARM’s v7/v8 ISA • Why can’t ARM partners sell servers? – 99%+ of laptops/desktops/servers are based on the AMD64 ISA (over 95%+ built by Intel) • How can IBM still sell mainframes? – IBM 360 is the oldest surviving ISA (50+ years) ISA is the most important interface in a computer system ISA is where software meets hardware 2 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

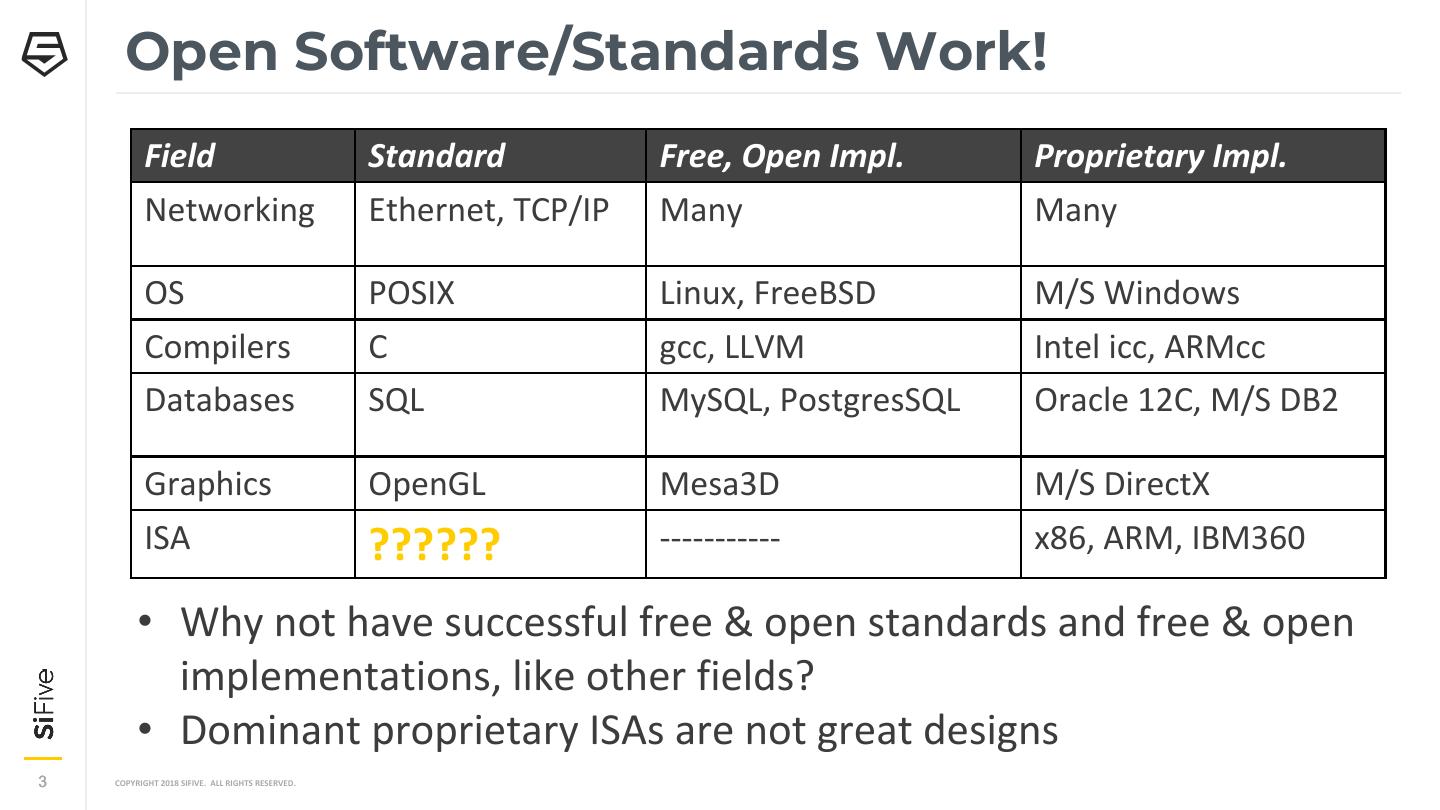

3 . Open Software/Standards Work! Field Standard Free, Open Impl. Proprietary Impl. Networking Ethernet, TCP/IP Many Many OS POSIX Linux, FreeBSD M/S Windows Compilers C gcc, LLVM Intel icc, ARMcc Databases SQL MySQL, PostgresSQL Oracle 12C, M/S DB2 Graphics OpenGL Mesa3D M/S DirectX ISA ?????? ----------- x86, ARM, IBM360 • Why not have successful free & open standards and free & open implementations, like other fields? • Dominant proprietary ISAs are not great designs 3 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

4 . What is RISC-V? • A high-quality, license-free, royalty-free RISC ISA specification originally designed at UC Berkeley • Standard maintained by the non-profit RISC-V Foundation • Suitable for all types of computing system, from microcontrollers to supercomputers • Numerous proprietary and open-source cores • Experiencing rapid uptake in industry and academia • Supported by a growing shared software ecosystem • A work in progress… 4 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

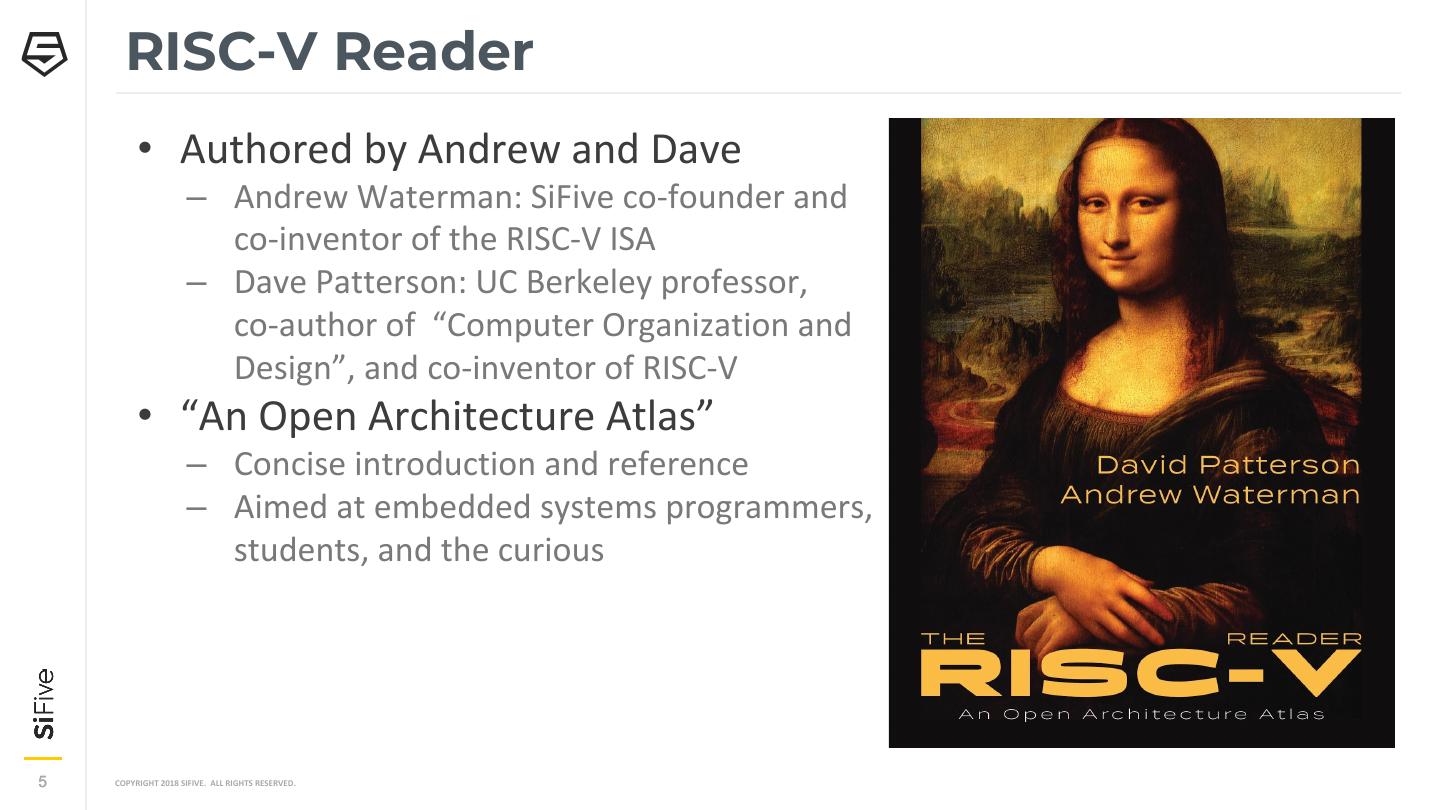

5 . RISC-V Reader • Authored by Andrew and Dave – Andrew Waterman: SiFive co-founder and co-inventor of the RISC-V ISA – Dave Patterson: UC Berkeley professor, co-author of “Computer Organization and Design”, and co-inventor of RISC-V • “An Open Architecture Atlas” – Concise introduction and reference – Aimed at embedded systems programmers, students, and the curious 5 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

6 .Origin of RISC-V COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

7 . RISC-V Origins • In 2010, after many years and many projects using MIPS, SPARC, and x86 as the bases of research at Berkeley, it was time to choose an ISA for next set of projects • Obvious choices: x86 and ARM 7 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

8 . Intel x86 “AAA” Instruction • ASCII Adjust After Addition • AL register is default source and destination • If the low nibble is > 9 decimal, or the auxiliary carry flag AF = 1, then – Add 6 to low nibble of AL and discard overflow – Increment high byte of AL – Set CF and AF • Else – CF = AF = 0 • Single byte instruction 8 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

9 . ARM v7 LDMIAEQ Instruction LDMIAEQ SP!, {R4-R7, PC} • LoaD Multiple, Increment-Address • Writes to 7 registers from 6 loads • Only executes if EQ condition code is set • Writes to the PC (a conditional branch) • Can change instruction sets • Idiom for "stack pop and return from a function call" 9 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

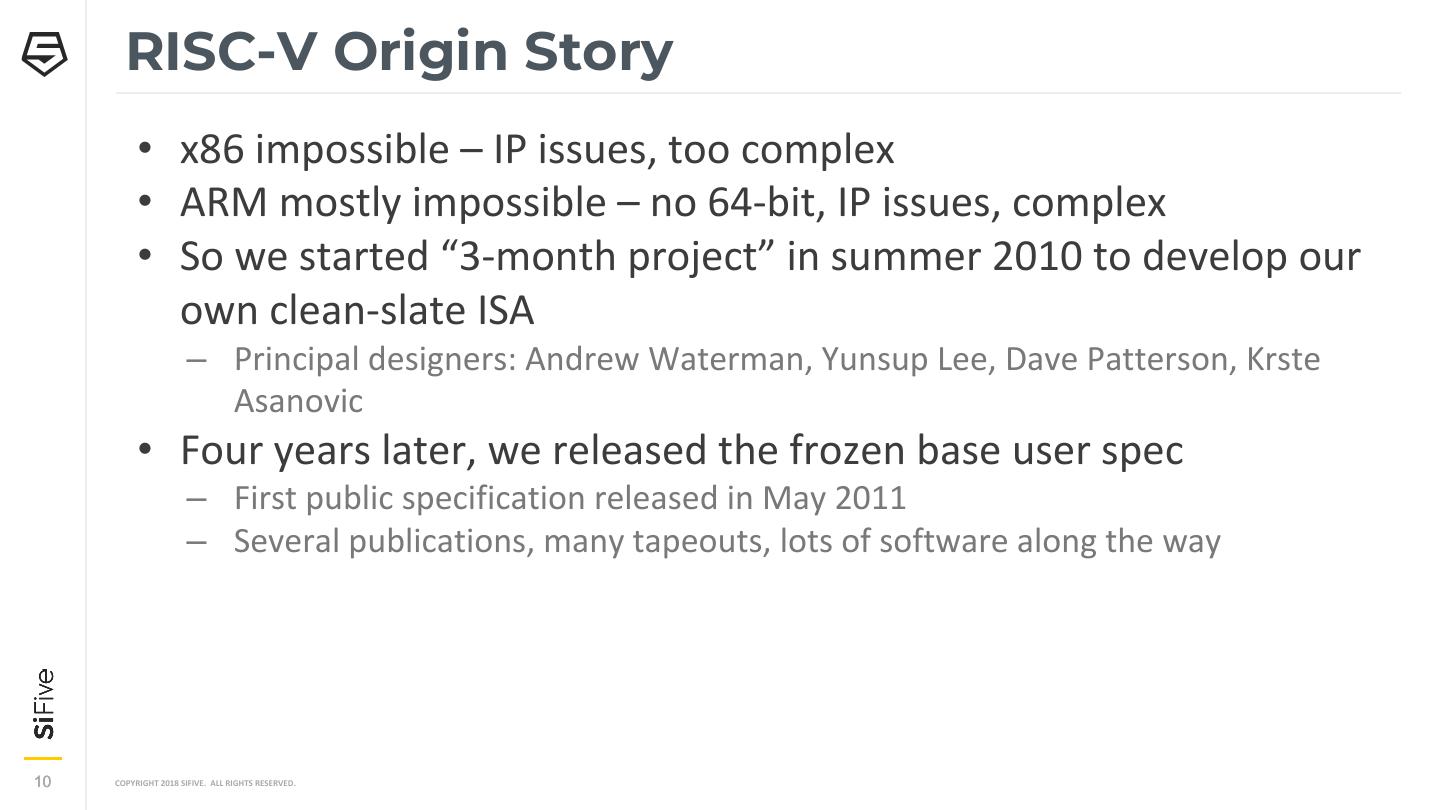

10 . RISC-V Origin Story • x86 impossible – IP issues, too complex • ARM mostly impossible – no 64-bit, IP issues, complex • So we started “3-month project” in summer 2010 to develop our own clean-slate ISA – Principal designers: Andrew Waterman, Yunsup Lee, Dave Patterson, Krste Asanovic • Four years later, we released the frozen base user spec – First public specification released in May 2011 – Several publications, many tapeouts, lots of software along the way 10 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

11 . Static Code Size • RISC-V is now the smallest ISA for 32- and 64-bit addresses • All results are with the same GCC compiler and options 11 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

12 . Dynamic Bytes Fetched • RV64GC is lowest overall in dynamic bytes fetched 12 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

13 . Silicon Implementations Hurricane-1 Hurricane-2 CRAFT Raven, Hurricane: ST 28nm FDSOI BROOM SWERVE, BROOM: TSMC 28nm EOS: IBM 45nm SOI, CRAFT: 16nm TSMC 13 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

14 . DIY Chip Tapeout Effort 14 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

15 . RISC-V Software 15 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

16 . There’s a lot of software! From: Palmer Dabbelt <palmer.dabbelt@eecs.berkeley.edu> To: config-patches@gnu.org Subject: config.sub patch for RISC-V Date: Wed, 10 Sep 2014 19:20:31 -0700 Message-Id: <1410402032-9184-1-git-send-email-palmer.dabbelt@eecs.berkeley.edu> X-Mailer: git-send-email 1.8.5.5 This patch provides support for the RISC-V ISA: http://riscv.org/ Not yet upstreamed ports of the binutils, GCC, LLVM, glibc, and Linux exist for RISC-V, and a number of hardware implementations exist -- more more information can be seen at http://riscv.org . We'd like to start getting RISC-V recognized by configure so it's easier for people to start porting stuff. Thanks! 16 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

17 .Current State of RISC-V COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

18 . RISC-V Foundation 18 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

19 . RISC-V Specifications • User Mode ISA Specification – RV32I/RV64I: ALU, branches, and memory – M extension for multiplication – A extension for atomics – F and D extensions for single and double precision floating-point – C extension for compressed instructions (16-bit) • Privileged Mode ISA Specification – Supervisor mode – Hypervisor mode – Machine mode • External Debug Specification – Debug machine-mode software over JTAG 19 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

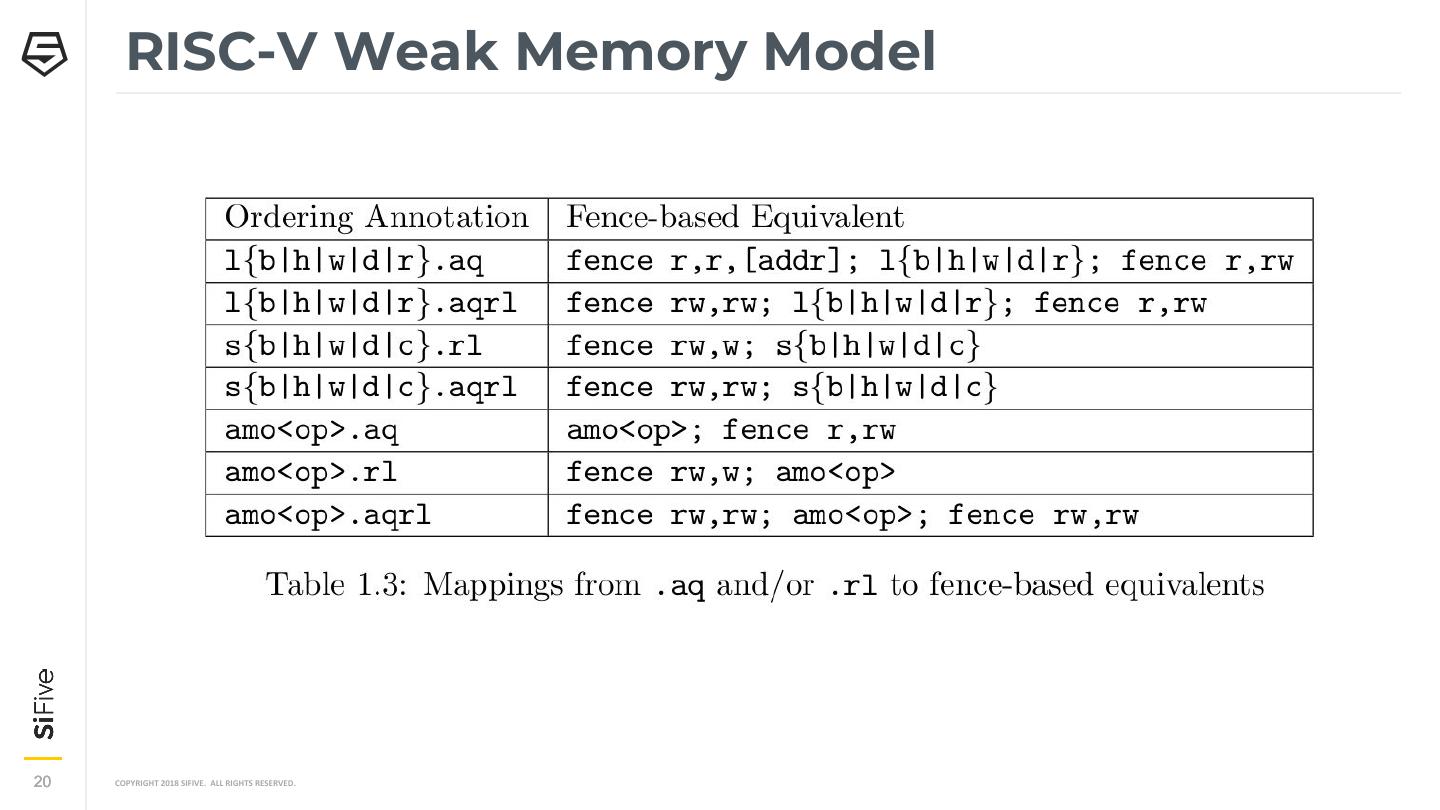

20 . RISC-V Weak Memory Model 20 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

21 . RISC-V Linux Kernel Port ● Upstream Kernel boots ○ Upstream boots on QEMU 21 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

22 . GNU-Based Toolchains ● binutils, GCC: May, 2017 ● glibc: February, 2018 ○ only supports rv64i-based ISAs ● newlib: August, 2017 ● “Probably not a compiler bug” 22 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

23 . Open Source Hardware ● Fedora runs on open source hardware ● Reproduced open-source FPGA shell ○ http://github.com/sifive/freedom 23 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

24 . Open Standards Work! • Kito Cheng (Andes Technology): GCC and newlib • Jim Wilson (SiFive): binutils and GCC • Darius Rad (Bluespec): glibc • Andrew Waterman (SiFive): binutils, GCC, and glibc • DJ Delorie (RedHat): glibc 24 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

25 . Zeyhpr ● http://docs.zephyrproject.org/boards/riscv32/index.html ● Upstream support for HiFive1 ● Zephyr SDK comes with RISC-V toolchains ● Used in a real product ○ http://badge.antmicro.com/ ● Released 1.13.0 recently 25 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

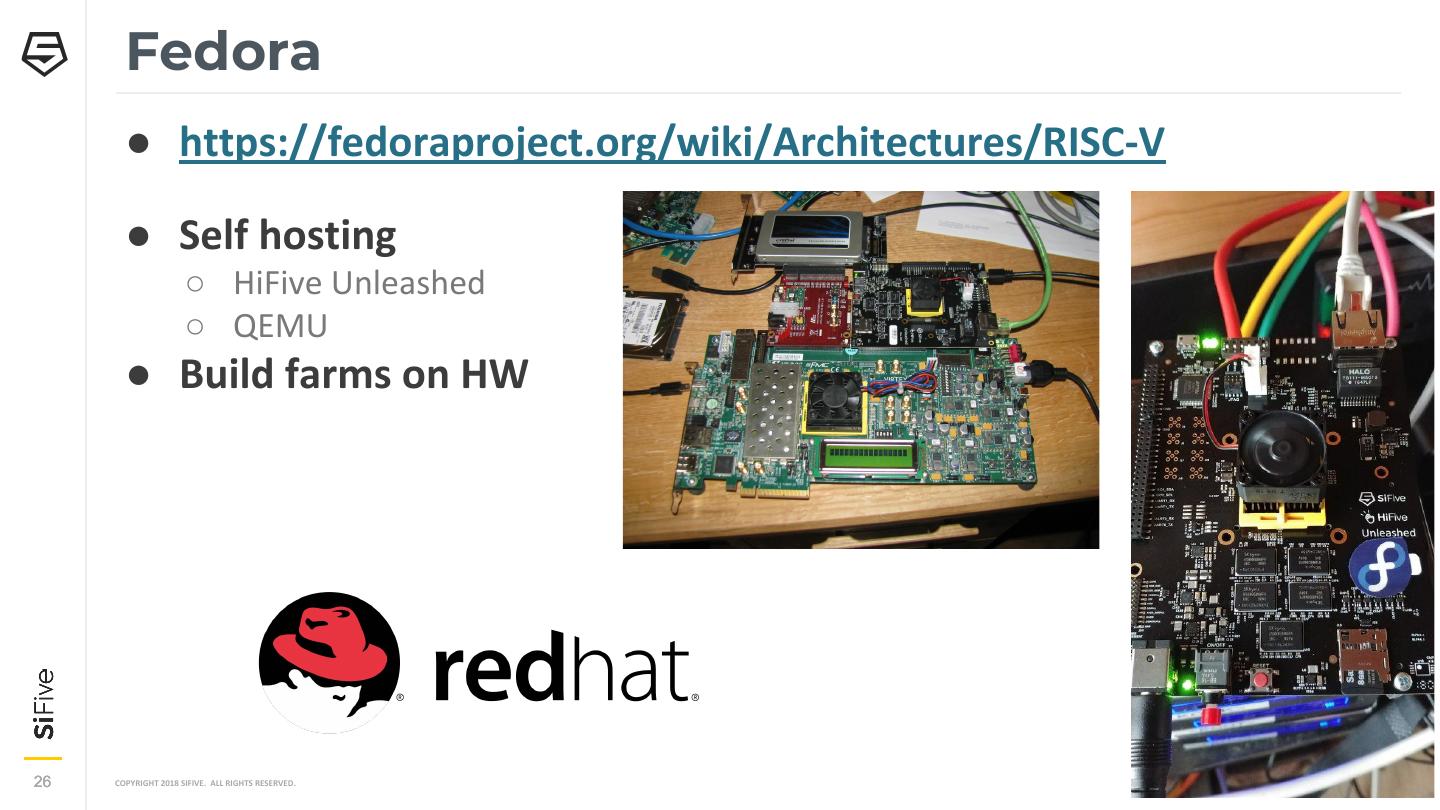

26 . Fedora ● https://fedoraproject.org/wiki/Architectures/RISC-V ● Self hosting ○ HiFive Unleashed ○ QEMU ● Build farms on HW 26 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

27 . Debian ● https://wiki.debian.org/RISC-V 27 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

28 . OpenEmbedded/Yocto ● https://github.com/riscv/meta-riscv ● Port is in good shape ○ Supported upstream, runs X ○ Works on HiFive Unleashed and QEMU ● Khem Raj gave a talk at ELC ○ https://www.youtube.com/watch?v=TdsmjqWJmfc 28 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.

29 . SiFive’s HiFive Unleashed ● 1.5GHz Quad Core on 28nm ● 2MiB L2 cache and 64-bit DDR4 ● ChipLink board-to-board interconnect 29 COPYRIGHT 2018 SIFIVE. ALL RIGHTS RESERVED.